# An Approach to the Design of Multistandard $\Sigma\Delta$ Modulators

A. MORGADO, J.M. DE LA ROSA, R. DEL RÍO, F. MEDEIRO, B. PÉREZ-VERDÚ, F.V. FERNÁNDEZ, AND A. RODRÍGUEZ-VÁZQUEZ Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC) Ed. CNM-CICA, Av. Reina Mercedes s/n, 41012 Sevilla SPAIN

*Abstract:* - This paper discusses issues concerning the design of cascade sigma-delta modulators intended for multistandard wireless receivers. Four standards are covered: GSM, Bluetooth, UMTS, and WLAN. A top-down design methodology is proposed to find out the optimum modulator topology in terms of circuit complexity and reconfiguration parameters. Several reconfiguration strategies are adopted at both architecture- and circuit-level in order to adapt the modulator performance to the standards requirements with adaptive power consumption. Time-domain behavioural simulations are shown to validate the presented approach.

Key-Words: - Data converters, Sigma-Delta, Wireless, Multistandard

# **1** Introduction

The growth of wireless communication technologies has prompted the emergence of multitude of new applications and standards. These new standards —like IEEE 802.11 WLAN and UMTS— are complementing rather than replacing the existing ones —such as GSM— giving rise to the so-called *universal* or *multistandard* transceivers. These systems are able to operate over a variety of specifications, thus benefiting of the different services and functions offered by co-existing wireless standards [1].

Multistandard transceivers need to be implemented by reconfigurable building blocks that can be adapted to each specification by adjusting their circuit parameters with adaptive power consumption. One of the most challenging building blocks is the <u>Analog-to-Digital Converter (ADC)</u>, because of the wide range of sampling rates and dynamic ranges required to digitize the signals of each individual standard [2].

Sigma-Delta Modulators ( $\Sigma\Delta Ms$ ) are good candidates for implementing the ADC in multistandard, multimode communication systems [3][4]. They combine redundant temporal data (*oversampling*) to reduce quantization noise and filtering (*noise shaping*) to push this noise out of the signal band. On the one hand, these characteristics result in high-performance, robust ADCs with lower sensitivity to circuitry imperfections than Nyquist-rate ADCs, thus making easier to include reconfigurability and programmability functions without significant performance degradation. On the other,  $\Sigma\Delta Ms$  trade analog accuracy by signal processing, thus facilitating their integration in modern deep-submicron VLSI technologies, more suited to implement fast digital circuits than precise analog functions. Several multistandard  $\Sigma \Delta M$  ICs have been reported up to now [5]-[9]. Most of them are based on reconfiguring architecture-level parameters (modulator order, oversampling ratio and/or number of bits of the internal quantizers), whereas less emphasis is normally put at circuit-level parameters.

This paper presents design considerations applicable to expandible cascade  $\Sigma \Delta Ms$  intended for multistandard receivers —covering GSM, Bluetooth, UMTS, and WLAN. A top-down design procedure is described from system-level to building-block level, putting special emphasis on optimizing the circuit design for different operation modes. To this purpose, different strategies are adopted at both architectureand circuit-level in order to fulfill specifications with minimum power consumption.

# 2 Modulator Specifications

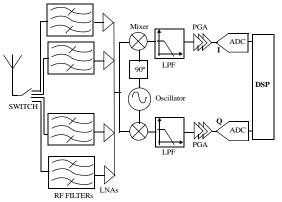

The  $\Sigma \Delta M$  in this paper has been designed to meet the requirements of <u>D</u>irect-<u>C</u>onversion <u>R</u>eceivers (DCRs) like that shown in Fig.1. This receiver architecture is commonly used in multistandard applications because it eliminates the need for both IF and image reject filtering and requires only a single oscillator and mixer [10]. In order to cope with the requirements of the different standards, separate (switchable) RF hardware paths (normally one per standard) are used whereas a single, digitally-programmed baseband section (from the mixer to the ADC) is implemented [11].

The receiver must detect a wanted signal at the antenna in presence of strong unwanted signals (*inter-feres*) without causing a degradation of the receiver performance. In multistandard implementations, the

receiver must fulfill the performance requirements of each standard [1]. Unfortunately, standards do not give explicit recommendations for the physical realization of the receivers. Instead of that, a black-box approach is assumed, and a set of evaluation tests are outlined to validate the receiver performance in terms of three basic aspects: *sensitivity*, *selectivity*, and *linearity* [12]. As an illustration, Table 1 summarizes the input-referred receiver requirements from these tests for the standards covered in this paper.

Receiver requirements are mapped onto building-block specifications (gain, dynamic range, linearity, and noise figure) in an iterative synthesis process, generally referred to as *receiver planning* [12]. This process is usually accompanied by a level diagram which shows how the different signals (wanted signal and interferes) evolve along the receiver chain.

In this paper, a simulation-based approach has

Fig. 1: Block diagram of a multistandard DCR.

Table 1: Input-referred requirements for the standards.

|                       | GSM     | Bluetooth | UMTS     | WLAN   |

|-----------------------|---------|-----------|----------|--------|

| Sensitivity           | -102dBm | -70dBm    | -117dBm  | -65dBm |

| Max. signal           | -15dBm  | -20dBm    | -25dBm   | -30dBm |

| Bandwidth             | 200kHz  | 1MHz      | 3.84MHz  | 20MHz  |

| Interferer level      | -49dBm  | -39dBm    | -46dBm   | -45dBm |

| Max. out-band blocker | 0dBm    | -10dBm    | -15dBm   | 0dBm   |

| Max. in-band blocker  | -23dBm  |           | -44dBm   | -30dBm |

| Max. adjacent channel | -33dBm  | -27dBm    | -92.7dBm | -65dBm |

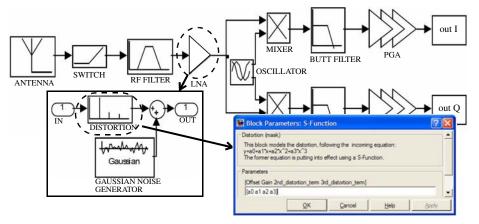

been adopted for the receiver planning. To this purpose, the receiver front-end building blocks have been modeled using MATLAB/SIMULINK as illustrated in Fig.2. Behavioral models of building blocks include the following design parameters:

- Operating frequency and bandwidth.

- Amplification within the passband of the block.

- Noise figure, represented as NF.

- Nonlinearity, commonly expressed by the input-referred 2nd- and 3rd-order intercept points.

In addition to these general parameters, some specific parameters have been also included, like for instance, oscillator phase noise and mixer offset.

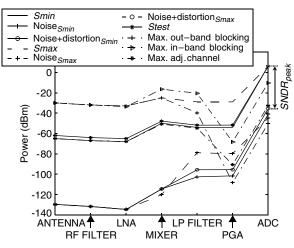

A complete receiver planning in which every building-block specification is a design parameter is beyond the scope of this work. Instead, fixed specifications extracted from reported radio receivers [13][14] were considered and the ADC effective resolution was extracted from an iterative simulation-based procedure considering the propagation of the different standard test signals through the receiver front-end. The outcome is shown in Table 2, which lists the ADC specifications for the different standards covered in this paper. As an illustration, Fig. 3 shows the level diagram for WLAN and depicts the propagation of the maximum and minimum signal (sensitivity) levels (Smax and Smin, respectively) from the antenna to the ADC input, together with that of noise and distortion. Note that the <u>Signal-to-(Noise+Distortion)-Ratio</u> (SNDR) peak at the ADC input is measured as the difference of *Smax* to the noise plus distortion. The test recommended by the standard with maximum spurious signals is also included, with *Stest* being the wanted signal level.

The specifications in Table 2 are the starting point for the modulator high-level synthesis, detailed below.

Table 2: ADC specifications.

| <b>L</b>   |        |           |         |       |  |  |  |

|------------|--------|-----------|---------|-------|--|--|--|

|            | GSM    | Bluetooth | UMTS    | WLAN  |  |  |  |

| Resolution | 13bit  | 11bit     | 9bit    | 7bit  |  |  |  |

| Bandwidth  | 200kHz | 1MHz      | 3.84MHz | 20MHz |  |  |  |

Fig. 2: Illustrating the behavioral model of the DCR in SIMULINK.

Fig. 3: Level diagram for WLAN.

# **3** Architecture Selection

#### 3.1 Expandible modulator architecture

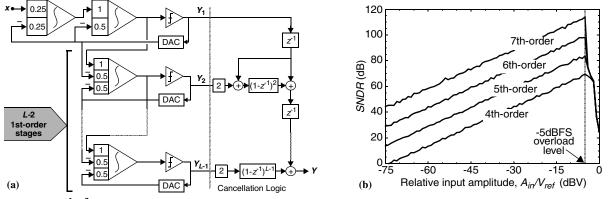

Given that reconfigurability issues must be boosted in the targeted multistandard application, the expandible  $\Sigma\Delta M$  in Fig.4*a* [15] has been selected. This cascade topology comprises a 2nd-order stage followed by 1st-order stages, and can be easily extended to build a  $\Sigma\Delta M$  of a generic order *L* by simply adjusting the number of 1st-order stages. Note that this architecture can exploit the benefits of an unconditionally stable high-order shaping thanks to the cascade structure and a robust, linear multibit quantization by incorporating it only in the modulator last stage.

Fig.4*a* depicts the selected set of integrator weights and the required digital cancellation logic in this architecture, henceforth called  $2-1^{L-2} \Sigma \Delta M$ . Altogether, the main advantages are [15]:

- The systematic loss of resolution that is typically present in every cascade  $\Sigma \Delta M$  in comparison with an ideal *L*-th order loop is only 6dB.

- The modulator overload level remains constant at -5dBFS, regardless the order of the expandible cascade. This feature is illustrated in Fig.4*b*.

- The output swing required in the integrators is only

the modulator reference voltage  $(\pm V_{ref})$ .

- The weights in the 1st-order stages can be distributed into only two SC branches.

- The total number of unit capacitors is only  $2 \times [5 + 4(L-1)]$ , what benefits area occupation, thermal noise, and amplifier dynamics.

- All 1st-order stages can be electrically identical<sup>†</sup>, what considerably simplifies the electrical and physical implementation of the modulator.

#### 3.2 Exploration of cascade candidates

Note that every cascade  $\Sigma \Delta M$  belonging to the family in Fig.4*a* can be univocally described by three parameters: the modulator order (*L*), the oversampling ratio (*OSR*), and the number of bits in the last stage (*B*). Thus, a {*L*, *B*, *OSR*} triad is used to codify them.

The first step in the design of the multistandard  $\Sigma\Delta M$  is the exploration of the {*L*, *B*, *OSR*} candidates for each standard that fulfill its corresponding requirements with minimum power consumption. At this step, an updated version of the analytical procedure described in [15] to estimate the power consumption of  $2 \cdot 1^{L-2}$   $\Sigma\Delta Ms$  has been followed. The procedure, based on compact expressions that contemplate both architectural and technological features, schematically consists of the following steps:

- 1) The in-band quantization error power  $(P_Q)$  is calculated for given values of  $\{L, B, OSR\}$  and  $V_{ref}$ . Noise leakages due to capacitor mismatch, finite amplifier DC gain, and errors in the multibit quantizer (if B > 1) are also contemplated.

- 2) The in-band error power due to circuit noise  $(P_{CN})$  is considered. The value of the sampling capacitor at the modulator front-end  $(C_S)$  is selected so that  $P_Q + P_{CN}$  is smaller than the maximum allowed total in-band error.  $P_{CN}$  will be mainly contributed by kT/C noise, but some room is left at this step

- †. If multibit quantization is used in the modulator last stage, its weights are usually doubled to easy the implementation of the corresponding ADC and DAC. This, together with the larger integrator load due to the ADC, normally prevents from using the same electrical design.

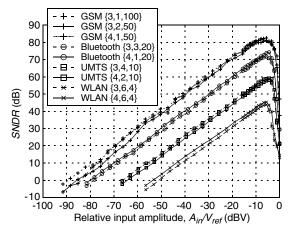

Fig. 4:  $2 - 1^{L-2} \Sigma \Delta M$ : (a) Block diagram; (b) Illustration of the constant overload level (*SNDR* curves for *OSR* = 16).

for the contribution of the front-end amplifier noise.

- 3) The amplifier <u>Gain-Bandwidth</u> product (*GB*) is estimated so that the in-band error power due to the integrator defective settling ( $P_{st}$ ) is non-limiting ( $P_{st} \ll P_Q + P_{CN}$ ). A linear settling model is used, considering that it takes a number  $\ln(2^{ENOB})$  of time constants to settle within *ENOB* resolution.

- 4) The amplifier *GB* is related to its power dissipation, for which the amplifier topology must be known a priori. Suitable candidates are closely related to the process technology —CMOS 0.13μm in our case— and its supply voltage, minimal device length, etc. Usual choices are folded cascodes for supplies above 3V or two-stage amplifiers below 2.5V.

- 5) Once the power dissipation of the front-end integrator has been estimated, that of the remaining ones (with less demanding specifications) is considered to be a fraction of it. The overall modulator power is then basically obtained by adding up all contributions, together with the dynamic power in the SC stages.

Given the targeted multistandard application, the suitable  $\{L, B, OSR\}$  triads for each standard have been explored under the following global constraints:

- The modulator reference is fixed to 1.2V in order to place the input signal level at -5.6dBFS and maximize the *SNDR* (see Fig.4*b*).

- Given the targeted range of resolutions ( $\leq 13$ bit), the explored values of L are restricted to 2, 3, and 4.

- In order to easy the frequency division of a master clock frequency from one standard to another, the sampling frequency  $(f_s)$  is restricted to values  $\div 1$ ,  $\div 2$ ,  $\div 4$ , etc., from a maximum of 160MHz. This limits the *OSR* values to explore and forces to expand the bandwidth in WLAN from 3.84MHz to 4MHz.

- The smallest value for the unit capacitor  $(C_u)$  is fixed to 0.25pF for mismatching issues.

- In order to easy the circuit reconfiguration, the sampling capacitor at the modulator front-end can only take values that are multiple of  $C_u$ .

Table 3 summarizes the ranking of  $\Sigma \Delta Ms$  with the lowest estimated power for each standard. Together with the values for {*L*, *B*, *OSR*}, those required for  $f_s$  and  $C_s$ , and the obtained Dynamic Range (*DR*) and *SNDR* peak are also enclosed. The highlighted rows in Table 3 correspond to the  $\Sigma \Delta Ms$  that we have selected for further consideration. Note that the rest of candidates are directly covered by the selected ones, since the former just imply an increase *L* or *B*. Thus, the selected  $\Sigma \Delta Ms$  at this step globally comprise:

- 3rd- and 4th-order cascades.

- Single-bit quantization and multibit quantization of 2, 3, 4, or 6 bits.

- Sampling frequencies of 20, 40, 80, or 160MHz.

- Sampling capacitors of 0.25pF or 0.5pF.

**Table 3:** Ranking of  $\Sigma \Delta Ms$  according to power estimations.

|           |    |     |       |               | e i     |       |                      |       |  |

|-----------|----|-----|-------|---------------|---------|-------|----------------------|-------|--|

| Standard  | L  | B   | OSR   | $f_s$         | $C_{S}$ | DR    | SNDR <sub>peak</sub> | Power |  |

| Stanuaru  | LD | USK | (MHz) | ( <b>pF</b> ) | (bit)   | (bit) | (mW)                 |       |  |

| GSM       | 4  | 1   | 50    | 20            | 0.50    | 14.42 | 13.59                | 10.9  |  |

|           | 3  | 2   | 50    | 20            | 0.50    | 14.39 | 13.56                | 11.7  |  |

|           | 3  | 3   | 50    | 20            | 0.50    | 14.41 | 13.58                | 12.5  |  |

|           | 4  | 2   | 50    | 20            | 0.50    | 14.42 | 13.59                | 13.4  |  |

|           | 3  | 4   | 50    | 20            | 0.50    | 14.41 | 13.58                | 14.1  |  |

|           | 4  | 3   | 50    | 20            | 0.50    | 14.42 | 13.59                | 14.2  |  |

|           | 4  | 4   | 50    | 20            | 0.50    | 14.42 | 13.59                | 15.8  |  |

|           | 3  | 1   | 100   | 40            | 0.25    | 14.42 | 13.59                | 17.0  |  |

|           | 4  | 1   | 100   | 40            | 0.25    | 14.42 | 13.59                | 20.0  |  |

| Bluetooth | 4  | 1   | 20    | 40            | 0.25    | 12.82 | 11.99                | 18.1  |  |

|           | 3  | 3   | 20    | 40            | 0.25    | 12.76 | 11.93                | 20.6  |  |

|           | 3  | 4   | 20    | 40            | 0.25    | 13.05 | 12.22                | 22.5  |  |

|           | 4  | 2   | 20    | 40            | 0.25    | 13.16 | 12.33                | 23.0  |  |

|           | 4  | 3   | 20    | 40            | 0.25    | 13.21 | 12.38                | 23.9  |  |

|           | 4  | 4   | 20    | 40            | 0.25    | 13.22 | 12.39                | 25.5  |  |

|           | 3  | 1   | 40    | 80            | 0.25    | 13.40 | 12.57                | 32.1  |  |

| UMTS      | 3  | 4   | 10    | 80            | 0.25    | 10.81 | 9.98                 | 37.3  |  |

|           | 4  | 2   | 10    | 80            | 0.25    | 10.45 | 9.62                 | 38.6  |  |

|           | 4  | 3   | 10    | 80            | 0.25    | 11.46 | 10.63                | 42.0  |  |

| WLAN      | 3  | 6   | 4     | 160           | 0.25    | 8.12  | 7.29                 | 70.9  |  |

| WLAN      | 4  | 6   | 4     | 160           | 0.25    | 8.57  | 7.74                 | 80.8  |  |

The former issues can be handled at circuit level by reconfiguring the last stage of the expandible cascade to either single-bit or multibit with programmable resolution, by dividing the master clock frequency by a factor 2, 4, or 8, and by using switchable capacitors at the modulator front-end, respectively.

Seeking for a single circuit that covers all the former possibilities can a priori be done, but such a large degree of freedom in the reconfigurability will considerably increase the circuit complexity. Thus, only one  $\{L, B, OSR\}$  triad will definitively be selected for each standard. However, given that the estimated power consumptions are not very different from one case to another, the final decision will be taken after extracting their complete set of building-block requirements using more accurate behavioral simulations.

### 4 High-Level Synthesis

The formerly selected candidates have been extensively simulated using SIMSIDES [16], a time-domain simulator for  $\Sigma \Delta Ms$  that includes accurate behavioral models for thermal noise, integrator defective settling, distortion, etc. The architecture specifications can be then mapped onto more refined building-block requirements such as amplifier DC gain, *GB*, <u>Slew Rate</u> (*SR*), equivalent input noise, switch on-resistance, etc.

The followed steps for this process are:

1) Validate that the  $\Sigma \Delta Ms$  selected from Table 3 achieve the required *DR* for each standard, taking into account quantization error and kT/C noise.

- 2) Determine the maximum equivalent input noise for each amplifier that does not degrade the formerly achieved performance.

- 3) Determine the required amplifier dynamics (*GB* and *SR*), taking into account settling errors during both the integration and sampling phases [17].

- 4) Refine the DC gain and *SR* requirements at each front-end integrator in order to limit the generated distortion near the modulator overload level.

At this step different amplifiers are considered for each integrator in order to gain insight on their individual needs. Once the final architecture is selected for each standard, the global amplifier specifications will be tried to be covered using reconfigurable amplifiers (in terms of bias currents and/or transistor sizings).

However, switches will not be reconfigured from one standard to another, so they must be sized at this step considering their slow-down effect on the integrators dynamics [18] and their generated dynamic distortion [19]. They have been sized to exhibit a maximum on-resistance around  $250\Omega$ , which does not to compromise performance in the different standards and avoids the use of clock-boosting techniques.

The requirements of the selected  $\Sigma\Delta Ms$  after the former fine-tuning process are summarized in Table 4, in terms of the amplifier equivalent input noise, DC gain, and dynamics for each integrator.

# **5** Simulation Results

Fig.5 depicts the *SNDR* curves obtained by behavioral simulation for the modulator sizings in Table 4. The  $\Sigma\Delta$ Ms exhibit an *SNDR* peak larger than 81dB for GSM, 71dB for Bluetooth, 58dB for UMTS, and 44dB for WLAN. Based on the results in Table 4, especially on those related to the amplifier dynamics, the final selection of the  $\Sigma\Delta$ M architecture is:

- For GSM: {3, 1, 100}

- For Bluetooth: {4, 1, 20}

- For UMTS: {4, 2, 10}

- For WLAN: {3, 6, 4}

**Fig. 5:** *SNDR* curves obtained by behavioral simulation after the fine tuning of building-block specifications.

| Bluetooth                                         | 100}                                  | Integrator<br>#1<br>#2<br>#3<br>#1<br>#2<br>#3<br>#1 | noise (nV/√Hz)<br>7.0<br>135.0<br>237.5<br>6.0<br>32.5 | <b>DC gain</b> 1500 250 250 700 | Transconductance<br>(mA/V)<br>0.26<br>0.42<br>0.19<br>0.42 | <b>Output current</b><br>(μ <b>A</b> )<br>150<br>130<br>60 | Equivalent<br>capacitive load (pF)<br>3.51<br>5.67 | <i>GB</i><br>(MHz)<br>11.9<br>11.7 | SR<br>(V/μs)<br>55.1<br>47.0 |

|---------------------------------------------------|---------------------------------------|------------------------------------------------------|--------------------------------------------------------|---------------------------------|------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------|------------------------------------|------------------------------|

| GSM {3, 2, 3<br>{4, 1, 3<br>{3, 3, 3<br>Bluetooth | , 50}                                 | #2<br>#3<br>#1<br>#2<br>#3                           | 7.0<br>135.0<br>237.5<br>6.0<br>32.5                   | 1500<br>250<br>250<br>700       | 0.26<br>0.42<br>0.19                                       | 150<br>130                                                 | 3.51                                               | 11.9                               | 55.1                         |

| GSM {3, 2, 3<br>{4, 1, 3<br>{3, 3, 3<br>Bluetooth | , 50}                                 | #2<br>#3<br>#1<br>#2<br>#3                           | 135.0<br>237.5<br>6.0<br>32.5                          | 250<br>250<br>700               | 0.42<br>0.19                                               | 130                                                        |                                                    |                                    |                              |

| GSM {3, 2, 3<br>{4, 1, 3<br>{3, 3, 3<br>Bluetooth | , 50}                                 | #3<br>#1<br>#2<br>#3                                 | 237.5<br>6.0<br>32.5                                   | 250<br>700                      | 0.19                                                       |                                                            | 5.67                                               | 11.7                               | 470                          |

| (4, 1, 1)<br>{4, 1, 1)<br>{3, 3, 1]<br>Bluetooth  |                                       | #1<br>#2<br>#3                                       | 6.0<br>32.5                                            | 700                             |                                                            | 60                                                         |                                                    |                                    |                              |

| (4, 1, 1)<br>{4, 1, 1)<br>{3, 3, 1]<br>Bluetooth  |                                       | #2<br>#3                                             | 32.5                                                   |                                 | 0.42                                                       |                                                            | 5.67                                               | 5.4                                | 21.7                         |

| (4, 1, 1)<br>{4, 1, 1)<br>{3, 3, 1]<br>Bluetooth  |                                       | #3                                                   |                                                        | 400                             |                                                            | 200                                                        | 3.70                                               | 18.1                               | 68.1                         |

| {4, 1, 3<br>{3, 3, 5<br>Bluetooth                 | 50}                                   |                                                      |                                                        | 400                             | 0.62                                                       | 130                                                        | 5.67                                               | 17.3                               | 47.0                         |

| {3, 3, 2<br>Bluetooth                             | 50}                                   | #1                                                   | 225.0                                                  | 250                             | 0.23                                                       | 130                                                        | 16.03                                              | 2.3                                | 25.1                         |

| {3, 3, 2<br>Bluetooth                             | 50}                                   |                                                      | 6.0                                                    | 800                             | 0.39                                                       | 200                                                        | 3.71                                               | 16.7                               | 67.9                         |

| {3, 3, 2<br>Bluetooth                             | 507                                   | #2                                                   | 12.5                                                   | 250                             | 0.86                                                       | 120                                                        | 5.67                                               | 24.2                               | 43.4                         |

| Bluetooth                                         |                                       | #3                                                   | 125.0                                                  | 250                             | 0.25                                                       | 170                                                        | 5.67                                               | 7.1                                | 61.5                         |

| Bluetooth                                         |                                       | #4                                                   | 212.5                                                  | 250                             | 0.23                                                       | 50                                                         | 5.67                                               | 6.5                                | 18.1                         |

| Bluetooth                                         |                                       | #1                                                   | 8.0                                                    | 2000                            | 1.36                                                       | 240                                                        | 3.51                                               | 61.8                               | 88.2                         |

|                                                   | {3, 3, 20}<br>Bluetooth<br>{4, 1, 20} | #2                                                   | 26.0                                                   | 550                             | 2.52                                                       | 300                                                        | 5.67                                               | 70.8                               | 108.5                        |

|                                                   |                                       | #3                                                   | 49.0                                                   | 350                             | 4.04                                                       | 1000                                                       | 16.03                                              | 40.1                               | 193.4                        |

| {4, 1, 2                                          |                                       | #1                                                   | 7.0                                                    | 2000                            | 1.25                                                       | 320                                                        | 3.51                                               | 56.8                               | 117.6                        |

| {4, 1,                                            |                                       | #2                                                   | 12.0                                                   | 350                             | 2.52                                                       | 300                                                        | 5.67                                               | 70.8                               | 108.5                        |

|                                                   |                                       | #3                                                   | 19.0                                                   | 400                             | 1.19                                                       | 750                                                        | 5.67                                               | 33.4                               | 271.2                        |

|                                                   |                                       | #4                                                   | 40.0                                                   | 300                             | 0.46                                                       | 375                                                        | 5.67                                               | 12.9                               | 135.6                        |

|                                                   |                                       | #1                                                   | 18.0                                                   | 2500                            | 2.39                                                       | 413                                                        | 3.53                                               | 107.6                              | 150.9                        |

| {3, 4,                                            | 10}                                   | #2                                                   | 12.0                                                   | 500                             | 6.40                                                       | 800                                                        | 5.70                                               | 178.8                              | 289.1                        |

| UMTS {4, 2, 10}                                   |                                       | #3                                                   | 35.0                                                   | 400                             | 13.26                                                      | 2550                                                       | 16.15                                              | 130.7                              | 492.6                        |

|                                                   |                                       | #1                                                   | 11.0                                                   | 1800                            | 2.62                                                       | 506                                                        | 3.53                                               | 118.3                              | 184.9                        |

|                                                   | 101                                   | #2                                                   | 18.0                                                   | 400                             | 6.19                                                       | 750                                                        | 5.70                                               | 172.9                              | 271.1                        |

|                                                   | 10}                                   | #3                                                   | 45.0                                                   | 450                             | 8.14                                                       | 1000                                                       | 5.70                                               | 227.4                              | 361.4                        |

|                                                   | -                                     | #4                                                   | 35.0                                                   | 450                             | 6.61                                                       | 1000                                                       | 16.15                                              | 65.2                               | 193.2                        |

| {3, 6, 4}                                         | #1                                    | 45.0                                                 | 1000                                                   | 8.78                            | 750                                                        | 3.65                                                       | 382.8                                              | 271.2                              |                              |

|                                                   | ,4}                                   | #2                                                   | 30.0                                                   | 1375                            | 21.50                                                      | 1700                                                       | 5.90                                               | 579.9                              | 610.9                        |

|                                                   |                                       | #3                                                   | 22.5                                                   | 675                             | 28.45                                                      | 7000                                                       | 16.83                                              | 269.1                              | 1351.8                       |

| WLAN                                              |                                       | #1                                                   | 45.0                                                   | 1500                            | 8.77                                                       | 825                                                        | 3.67                                               | 380.1                              | 299.0                        |

| (4.7                                              | · 4)                                  | #2                                                   | 17.0                                                   | 1000                            | 24.29                                                      | 1600                                                       | 5.93                                               | 651.8                              | 577.4                        |

| {4, 6,                                            | {4, 6, 4}                             | #3                                                   | 20.0                                                   | 525                             | 17.29                                                      | 2750                                                       | 5.93                                               | 464.0                              | 992.4                        |

|                                                   |                                       | #4                                                   | 47.5                                                   | 650                             | 19.26                                                      | 3150                                                       | 16.95                                              | 180.9                              | 607.7                        |

**Table 4:** Amplifier requirements after fine tuning of the different  $\{L, B, OSR\}$  candidates.

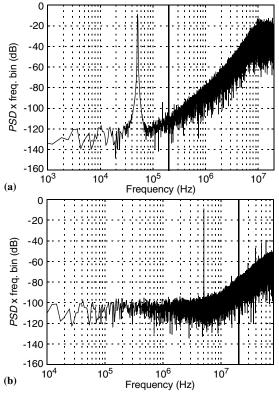

**Fig. 6:** Modulator output spectra obtained by behavioral simulation for: (a) GSM; (b) WLAN.

The selected  $\{L, B, OSR\}$  triads have also the advantage of requiring the same sampling capacitor (0.25pF —see Table 3), thus eliminating the need for switchable capacitor arrays at the modulator front-end.

Fig.6 shows the modulator output spectra obtained by behavioral simulation for GSM and WLAN.

### 6 Conclusions

A design methodology for the design of multistandard cascade  $\Sigma\Delta$  modulators has been described. Both architecture and circuit-level reconfiguration strategies have been considered in order to find out the optimum architecture in terms of power dissipation and silicon area. As an application of the proposed methodology, the high-level design of a cascade  $\Sigma\Delta$ modulator has been presented to cope with the requirements of several wireless standards.

This work has been supported by the Spanish Ministry of Science and Education (with support from the European Regional Development Fund) under contract TEC2004-01752/MIC.

References:

[1] X. Li and M. Ismail: *Multi-standard CMOS wireless* receivers: analysis and design. Kluwer Academic Pub-

lishers, 2002.

- [2] K. Gulati and H.S. Lee: "A Low-Power Reconfigurable Analog-to-Digital Converter". *IEEE J. of Solid-State Circuits*, Vol. 36, pp. 1900-1910, Dec. 2001.

- [3] K.T. Tiew et al.: "MASH Delta-Sigma Modulators for Wideband and Multi-Standard Applications", Proc. IEEE Int. Symp. on Circuits and Systems, pp. IV.778-781, 2001.

- [4] B.J. Farahani and M. Ismail: "A Low Power Multi-Standard Sigma-Delta ADC for WCDMA/GSM/Bluetooth Applications", Proc. IEEE Northeast Workshop on Circuits and Systems, pp. 241-243, 2004.

- [5] T. Burger and Q. Huang: "A 13.5mW 185-Msample/s ΔΣ Modulator for UMTS/GSM Dual-Standard IF Reception". *IEEE J. of Solid-State Circuits*, Vol. 36, pp. 1868-1878, Dec. 2001.

- [6] G. Gomez and B. Haroun: "A 1.5V 2.4/2.9mW 79/50dB DR ΣΔ Modulator for GSM/WCDMA in a 0.13µm Digital Process". Proc. IEEE Int. Solid-State Circuits Conf., pp. 1.306-307, 2002.

- [7] L. Gardelli *et al.*: "Tunable Bandpass Sigma-Delta Modulator Using One Input Parameter". *Electronics Letters*, Vol. 39, no. 2, pp. 187-189, Jan. 2003.

- [8] T.M.R. Miller and C.S. Petrie: "A Multibit Sigma-Delta ADC for Multimode Receivers". *IEEE J. of Solid-State Circuits*, Vol. 38, pp. 475-482, March 2003.

- [9] T.O. Salo *et al.*: "80-MHz Bandpass ΔΣ Modulators for Multimode Digital IF Receivers". *IEEE J. of Solid-State Circuits*, Vol. 38, pp. 464-474, March 2003.

- [10]A.A. Abidi: "Direct-conversion radio transceivers for digital communications". *IEEE J. of Solid-State Circuits*, Vol. 30, pp. 1399-1410, Dec. 1995.

- [11]A. Savla *et al.*: "A reconfigurable low IF-zero IF receiver architecture for multi-standard wide area wireless networks". *Proc. IEEE Int. Conf. on Electronics, Circuits and Systems*, pp. 935-937, 2003.

- [12]J. Crols and M. Steyaert: "CMOS Wireless Transceiver Design". Kluwer Academic Publishers, 1997.

- [13]H.-K. Yoon and Mohamed Ismail: "A CMOS Multi-standard Receiver Architecture for ISM and UNII Band Applications". Proc. IEEE Int. Symp. on Circuits and Systems, pp. IV.265-268, 2004.

- [14]E. Colin and L. Naviner: "On Baseband Considerations for Multistandard RF Receivers". Proc. IEEE Int. Conf. on Electronics, Circuits and Systems, pp. 691-694, 2003.

- [15]F. Medeiro *et al.*: "High-Order Cascade Multi-bit  $\Sigma \Delta$ Modulators". Chapter 9 at *CMOS Telecom Data Converters*. Kluwer Academic Publishers, 2003.

- [16]J. Ruiz-Amaya *et al.*: "An Optimization-based Tool for the High-Level Synthesis of Discrete-time and Continuous-Time ΣΔ Modulators in the MAT-LAB/SIMULINK Environment". *Proc. IEEE Int. Symp. Circuits and Systems*, pp. V.97-100, 2004.

- [17]R. del Río *et al.*: "Reliable analysis of settling errors in SC integrators: application to ΣΔ modulators". *Electronics Letters*, Vol. 36, n. 6, pp. 503-504, March 2000.

- [18]R. del Río *et al.*: "Highly Linear 2.5-V CMOS ΣΔ Modulator for ADSL+". *IEEE Trans. on Circuits and Systems I*, Vol. 51, pp. 47-62, Jan. 2004.

- [19]W. Yu et al.: "Distortion Analysis of MOS Track-and-Hold Sampling Mixers Using Time-Varying Volterra Series". *IEEE Trans. on Circuits and Systems II*, Vol. 46, pp. 101-113, Feb. 1999.