## Design Optimization of Discrete-time Single-Loop Sigma-Delta ADCs

## via Nonideality and Power Analyses

FU-CHUANG CHEN and MENG-SYUE LI

Dept. of Electrical and Control Engineering

National Chiao Tung University

Hsinchu 30050

Taiwan, R.O.C.

fcchen@cc.nctu.edu.tw

Abstract: - A conventional  $\Sigma\Delta$  ADC design approach is a time consuming process and needs much trials and errors. An optimization algorithm for the discrete-time single-loop  $\Sigma\Delta$  ADCs design is proposed. Circuit nonideality models are derived in output noise power forms through a systematic circuit imperfection study. A power model is also presented in order to estimate relative power consumption. These models reveal that design parameter variation can potentially affect several noises and errors in different ways, and may change system power consumption. This design complexity is qualitatively summarized into a table. Model completeness allows us to propose an optimization algorithm to search globally for a design parameter combination which meets SNR requirement while minimizing power consumption. Our optimization algorithm is tested against two published design results, and is verified by behavior simulations. Comparisons with behavioral-simulation-based optimization approaches are also made.

Key-Words: - Sigma delta modulator, noise model, power model, optimization

### 1 Introduction

$\Sigma\Delta$  modulators are widely used for high-resolution analog-to-digital conversion applications, achieving resolutions up to 12~20 bits. The earlier focus is on low to medium speed applications, such as audio [1, 2, 3], voice codec, and DSP chip [4, 51, 52, 53]. Recently, ΣΔ ADCs have been applied to higher bandwidth signals, and low power designs are frequently emphasized. For example, in ×DSL [5, 6] applications, signals up to 2.2MHz must be handled. Since significantly increasing the sampling rate is difficult, designers either seek to increase the order or the cascade stages [7, 8, 9], or employ multi-bit quantization [10, 11], or both, in order to achieve the required dynamic range. DAC linearity can be improved due to process technology advances, making the multi-bit architecture more popular. New technologies also help reduce power consumption [12]. The  $\Sigma\Delta$  modulator design is a complex and a time consuming process, because many coupled design parameters must be determined. Coming up with an acceptable design is challenging with increasing specification demands. Even an acceptable design may not be the best one. The paper proposes an optimization approach to increase automation and reduce complexity in single-loop  $\Sigma\Delta$  ADCs design.

To propose an optimization algorithm for single-loop  $\Sigma\Delta$  modulators, we need a complete set of important nonideality models and the power consumption model. Some issues concerning  $\Sigma\Delta$ modulator noise and error modelling appeared in [2, 3, 13-22]. System simulation tools were proposed in [13] and [22]. The results in [14-16] are not expressed in noise power forms, so relations between circuit parameters and noise powers are not clear. Reference [17] worked on the settling noise and the thermal noise, but certain settling error assumptions are not general enough to handle multi-bit cases. Results in [19] [20] focus on device noises such as thermal noise and flicker noise. Flicker noise is not considered in this work because it is affected by factors less correlated to the  $\Sigma\Delta$ modulator circuit parameters treated in this paper. The available models discussed above are either incomplete, or not in the form we require. In section II, we will elaborate on settling noise, DAC noise, OTA thermal noise, and reference voltage thermal noise. We will also categorize all major nonidealities into five parts, and express their

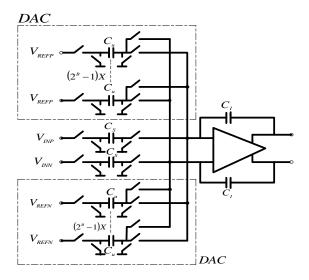

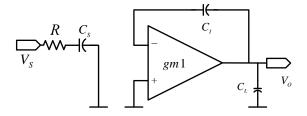

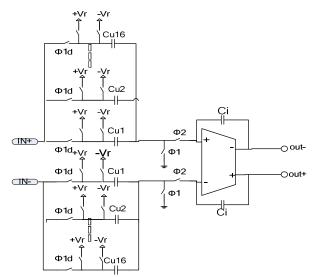

Fig. 1 Integrator and the DAC branches

models in noise power forms under a multi-bit setup. Power consumption models for  $\Sigma\Delta$  modulator analog, digital and multi-bit quantizer parts [23, 24, 25] will also be given.

An optimization design scheme is proposed in section III. It essentially combines system and circuit level designs, and optimizes all design parameters at the same time. This paper works on optimization of SNR, not SNDR. Nonlinear distortions are not considered in this paper. There exist applications where nonlinear distortions are often neglected. For example, in low-frequency, high resolution applications such as sensor signal conversion, people consider SNR only, and SNDR is not needed. The design optimization scheme is verified in section IV, and comparisons with behavior-simulation-based optimization schemes [48, 49] are also discussed. Conclusions are presented in section V. Then a nonlinear settling distortion analysis is given in the Appendix A to resolve issues in Section IV. Finally several modified noise power models for the circuit structure of [28] are provided in Appendix B.

#### 2 Problem Formulation

Proposing an optimization algorithm for searching design parameters which maximizes  $\Sigma\Delta$  ADC SNR while minimizing power consumption is one of the primary purposes in this paper. Model completeness determines success of this goal. The  $\Sigma\Delta$  modulator nonidealities are categorized into five parts in this section: finite OTA gain error, thermal noise, settling error, multi-bit DAC noise, and jitter noise. All nonideality models are expressed in noise power

forms, which can directly add to ideal quantizationnoise power. All noise power models discussed in the following are based on the integrator scheme, as shown in Fig.1. In Fig. 1,  $C_u$  is the unit capacitor whose capacitance is  $\frac{C_s}{2^B}$ . The power consumption model is presented as the last

## 2.1 Finite OTA Gain Error

part of this section.

For a general single-loop nth order  $\Sigma\Delta$  modulator with finite OTA gain A, the modified quantization noise is expressed as [18]

$$P_{Q(\text{mod.})} \cong \frac{\Delta^{2}}{12} \cdot \left[ \frac{\pi^{2n}}{(2n+1) \cdot OSR^{2n+1}} + \left( \frac{a_{1}}{A} \right)^{2} \cdot \frac{\pi^{2n-2} \cdot n}{(2n-1) \cdot OSR^{2n-1}} \right]$$

$$= P_{Q} + P_{AV} \tag{1}$$

where  $P_Q$  is the original quantization noise,  $a_1$  is the gain of the integrator at the first stage, and  $\Delta$  is the quantizer step size. The  $P_{AV}$  in (1) is due to finite OTA gain, and can be considered as an additive quantization noise power.

# 2.2 Thermal Noise (Switch, OTA, Reference circuits)

There are three thermal noise sources in the  $\Sigma\Delta$  modulator, in MOS switches, OTAs and reference voltage. The analyses are shown separately as follows. The total output switches thermal noise power from the switched capacitor integrator is [18, 23]

$$P_{sw} \cong \frac{1}{OSR} \cdot \left(\frac{8kT}{C_s}\right) \tag{2}$$

Half of  $P_{sw}$  is from the input branch, and the other half is from the DAC branch.

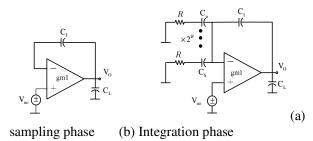

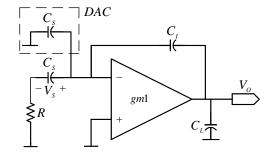

The OTA transistor thermal noise can be modeled as an equivalent noise source  $V_{no}$  at OTA input shown in Fig.2. In deep submicron process  $V_{no} \cong \frac{\alpha \cdot 10 \text{kT}}{\text{gm1}} \text{ V}^2/\text{Hz}$  [26], thermal noise power at

integrator output in the sampling phase is

$$P_{OTA}(samp) \cong V_{no} \cdot \frac{GBW_{samp}}{A \cdot 2\pi} \cdot \frac{\pi}{2} = \frac{10\alpha \cdot kT}{4AC_{r}}$$

(3)

Fig. 2 Equivalent circuits of sampling and integration phases

During the integration phase (Fig. 2(b)), the circuit looks

like a non-inverting amplifier, with

$$\frac{\mathbf{V}_{\mathrm{O}}}{\mathbf{V}_{\mathrm{no}}}(s) \cong \begin{pmatrix} 2a_{1} + 1 + 2sC_{s}R \\ 1 + 2sC_{s}R \end{pmatrix} \begin{pmatrix} 1 + \frac{s}{GBW_{A}} \end{pmatrix}$$

(4)

The OTA noise power at the first integrator output can be expressed as

$$P_{OTA}(\text{int}) \cong \int_0^\infty V_{\text{no}} \cdot \left| \frac{V_0}{V_{\text{no}}} (f) \right|^2 df$$

(5)

Finally, the total OTA thermal noise power at the  $\Sigma\Delta$  ADC output can be obtained as

$$P_{OTA} = \frac{1}{OSR} \cdot \left(\frac{1}{a_1}\right)^2 \cdot \left(P_{OTA}(samp) + P_{OTA}(int)\right)$$

$$= \frac{1}{OSR \cdot a_1^2} \cdot \left( \frac{10\alpha \cdot kT}{4AC_L} + \int_0^\infty V_{\text{no}} \cdot \left| \frac{V_{\text{o}}}{V_{\text{no}}} (f) \right|^2 df \right)$$

(6)

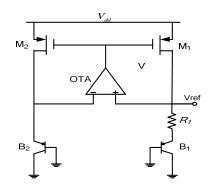

Consider the bandgap reference circuit in Fig. 3 [27]. Reference output noise is nearly equivalent to OTA input referred noise [27], so it can be expressed as  $\overline{V_{ref}}^2 \approx V_{no} = \frac{10 kT \cdot \alpha}{gm1}$ . Different

integrator schemes can introduce reference noise in different ways [5, 11, 28]. The case shown in Fig. 4 is considered, where this noise is introduced only in the sampling phase. If the reference noise is unbuffered, its noise power at the  $\Sigma\Delta$  ADC output can be derived as

$$P_{ref} = \frac{1}{OSR} \cdot \int_0^\infty \frac{\overline{V_{ref}}^2}{1 + 4\pi^2 R^2 C_c^2 f^2} df = \frac{\overline{V_{ref}}^2}{OSR \cdot 4RC_c}$$

(7)

Fig. 3 A bandgap voltage reference circuit

Fig. 4 Equivalent circuit while considering reference voltage noise

It's usual to add buffers between the bandgap circuits [29] and the DAC paths. Denote the 3dB buffer bandwidth as  $BW_b$ . If  $BW_b$  is smaller than  $\frac{1}{4RC}$ ,  $P_{ref}$  in (7) is changed to be  $P_{ref} = \overline{V_{ref}}^2 \cdot \frac{\pi \cdot BW_b}{2 \cdot OSR}$ . If  $BW_b$  is larger than  $\frac{1}{4RC}$ , (7) is applied.

## 2.3 Settling Error

As  $\Sigma\Delta$  modulator sampling frequency increases, and multi-bit quantization becomes a high resolution and high-speed application trend, the dynamic settling problem of switched capacitor integrator becomes a more dominant factor. Previous articles have mentioned the settling error [14, 21, 30]. References [14] and [30] provide behavior models, which are tedious and integrate poorly with noisepower models of other noises or errors. The noisepower model of [21] is very primitive since it assumes the p.d.f.(probability density function) settling error is uniformly distributed, and does not consider multi-bit quantization. We only consider the integrator at the first stage. Settling errors at later stages are less influential due to noise shaping. Now consider a switched capacitor integrator in Fig. 5. Assume the MOS switch has an on-resistance R, and gm1 is the transconductance of

(a) Sampling phase

## (b) Integration phase

Fig. 5 Switched capacitor integrator diagrams OTA. Let the output parasitic capacitor  $C_L \cong \eta \cdot C_I$ , where  $\eta$  is the parasitic percentage of bottom plate, assumed to be 20% [31]. In Fig. 5(a), the voltage  $V_s$  represents the difference between the sinusoid input signal and the feedback signal from DAC. It is sampled by  $C_s$ ,  $C_s$  is charged in the half clock period  $\frac{T}{2}$  to the voltage  $V_{cs}$ :

$$V_{CS} = V_S \cdot [1 - \exp(-\frac{T}{2 \cdot \tau_1})] \tag{8}$$

where  $\tau_1 = R \cdot C_s$  is the time constant in the input branch. So the setting error during the sampling phase is:

$$\varepsilon_1 = V_s \cdot \exp(-\frac{T}{2 \cdot \tau_1}) \tag{9}$$

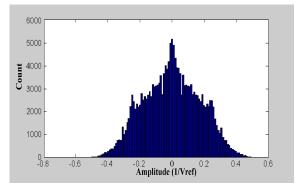

In order to obtain settling noise power during the sampling phase from (9), we need to find the  $V_s$  statistical property. Simulations results (using SIMULINK) on a second-order  $\Sigma\Delta$  modulator with  $a_1 = 0.5$ ,  $a_2 = 2$ , 10-level quantization, reference voltage  $V_{ref} = \pm IV$ , and a full scale sinusoidal input signal, are shown in Fig. 6. The result is close to a Gaussian distribution. Therefore, we assume  $V_s$  is

Gaussian distributed with a zero mean. The standard deviations  $\sigma_{VS}$  of  $V_S$  under different quantizer levels are tabulated in Table I. We observed that when the

Fig. 6 Simulated results of  $V_s$  distribution quantizer level N increases,  $\sigma_{vs}$  decreases. From this table, the relation between standard deviation  $\sigma_{vs}$  and quantizer levels  $2^B$  can be approximated by

$$2^{B} \cdot \sigma_{VS} \approx 1.4 \cdot \left| V_{ref} \right| \tag{10}$$

The settling noise can reasonably assumed to be white, and its power spectral density constant and distributed over  $(-f_s/2, f_s/2)$  as

$$S_{\varepsilon 1} = \frac{1}{f_S} \cdot \left(\frac{1.4 \cdot V_{ref}}{2^B}\right)^2 \cdot \exp(\frac{-T}{\tau_1}) \tag{11}$$

Due to oversampling, noise power can be obtained by integrating (11) in the signal band  $(-f_B, f_B)$ , which is

$$P_{\varepsilon_1} = \frac{1}{OSR} \cdot \left(\frac{1.4 \cdot V_{ref}}{2^B}\right)^2 \cdot \exp(\frac{-T}{\tau_1})$$

(12)

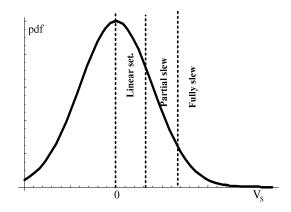

Next, we consider the integration phase shown in Fig.5 (b), where the  $2^B$  unit capacitors are combined into  $C_s$ , and the  $2^B$  DAC switches are neglected. The charge stored in sampling capacitor will be added to the integration capacitor and this charge current is supplied by OTA. So when the slew rate and gain bandwidth are not large enough, the settling error  $\varepsilon_2$  will be produced. The statistical properties of  $V_s$  have been summarized in Table I. Then, according to Fig. 7, three types of settling conditions can happen in the integrator output during this phase, and the corresponding voltage errors of these three conditions are [14].

#### 2.1.1 Linear settling

When the initial change rate of the integrator output voltage  $(V_a)$  is smaller than the OTA slew rate (SR).

| Std. deviation $(\sigma_{VS})$ | Variance | Quantizer<br>level (N) | Bit<br>number<br>(B) |

|--------------------------------|----------|------------------------|----------------------|

| 0.706                          | 0.498    | 2                      | 1                    |

| 0.476                          | 0.227    | 3                      | 1.585                |

| 0.282                          | 0.080    | 5                      | 2.322                |

| 0.198                          | 0.040    | 7                      | 2.808                |

| 0.152                          | 0.023    | 9                      | 3.17                 |

| 0.124                          | 0.016    | 11                     | 3.46                 |

| 0.047                          | 0.002    | 31                     | 4.95                 |

TABLE I Standard deviations of  $V_s$  v.s. different quantizer bit numbers

$$\varepsilon_2 = a_1 \cdot |V_S| \cdot \exp(\frac{T}{2 \cdot \tau_2})$$

, when  $0 < |V_S| < \frac{1}{a_1} \cdot SR \cdot \tau_2$  (13)

#### 2.1.2 Partial slewing

The initial change rate of  $V_o$  is larger than SR, but it gradually decreases until it is below the slew rate.

$$\varepsilon_2 = SR \cdot \tau_2 \cdot \exp(\frac{a_1 \cdot |V_S|}{SR \cdot \tau_2} - \frac{T}{2\tau_2} - 1)$$

$$, \text{when } \frac{1}{a_1} \cdot SR \cdot \tau_2 < |V_S| < (\frac{T}{2} + \tau_2) \frac{SR}{a_1}$$

$$(14)$$

### 2.1.3 Fully slewing

The initial change rate of  $V_o$  is larger than SR, and it maintains above SR in the T/2 interval.

$$\varepsilon_2 = a_1 \cdot |V_S| - SR \cdot \frac{T}{2}$$

,when  $|V_S| > \frac{SR}{a_1} (\frac{T}{2} + \tau_2)$  (15)

where SR is the slew rate of OTA, and  $\tau_2 = \frac{1 + 2\pi \cdot GBW \cdot R \cdot C_s}{2\pi \cdot GBW}$  [32] is the time constant in

the integration phase, with *GBW* being the equivalent gain bandwidth in the integration phase. The capacitor loading in OTA output during this

phase is heavier than in the sampling phase, and is [23]

$$C_{L2} = 2C_S + C_L \cdot \frac{C_I + (2C_S)}{C_I} \tag{16}$$

the GBW is given by

$$GBW = \frac{gm1}{C_{1.2} \cdot 2\pi} \tag{17}$$

Fig. 7 Three types of settling conditions in integration phase

In order to estimate settling noise in this phase, we must analyze the occurrence probability for each of the three conditions defined by (13)-(15). The probability of  $V_s$  in the linear settling region is

$$Pr_{lin} = \int_{0}^{\frac{1}{a_{1}}SR \cdot \tau_{2}} \frac{2}{\sqrt{2\pi} \cdot \sigma_{VS}} \exp(\frac{-V_{S}^{2}}{2 \cdot \sigma_{VS}^{2}}) dV_{S}$$

$$= Erf\left[\frac{SR\tau_{2}}{\sqrt{2}a_{1}\sigma_{VS}}\right]$$

(18)

Let  $\varepsilon_{2\text{max}}$  be the maximum linear settling error, and it can be obtained by substituting  $|V_S| = \frac{1}{a_1} \cdot SR \cdot \tau_2$

into equation (13). Since  $V_s$  is approximately Gaussian, it is reasonable to assume that the linear settling error in (13) also has a Gaussian distribution in  $\left(-\varepsilon_{2\max}, \varepsilon_{2\max}\right)$ . So the average linear settling noise power in the integration phase is approximately

$$P_{lin} \approx \frac{\varepsilon_{2 \max}^2}{9} = \frac{1}{9} \left( SR \cdot \tau_2 \exp(\frac{-T}{2\tau_2}) \right)^2$$

(19)

Before calculating the partial settling probability, we must check the possibility of this condition. If  $\frac{1}{a_1} \cdot SR \cdot \tau_2 \geq 2V_{ref} \quad , \quad \text{a partial and fully slewing}$  condition does not need to be considered. If

$\frac{1}{a_1} \cdot SR \cdot \tau_2 < 2V_{ref}$ , partial slewing probability is

$$Pr_{par} = Erf\left[\frac{SR(T+2\tau_2)}{2\sqrt{2}a_1\sigma_{VS}}\right] - Erf\left[\frac{SR\tau_2}{\sqrt{2}a_1\sigma_{VS}}\right]$$

(20)

Now we calculate noise power under the partial slewing condition. The pdf of  $V_s$  is

$$f_{par}(V_S) = \frac{1}{\Pr_{par}} \cdot \frac{2}{\sqrt{2\pi} \cdot \sigma_{VS}} \exp(\frac{-V_S^2}{2 \cdot \sigma_{VS}^2})$$

(21)

when

$$\frac{1}{a_1} \cdot SR \cdot \tau_2 < |V_S| < (\frac{T}{2} + \tau_2) \frac{SR}{a_1}$$

.

The  $\varepsilon_2$  here is no longer Gaussian distributed, and its pdf

can be computed from

$$f_{par}(\varepsilon_2) = f_{par}(V_S) \cdot \frac{dV_S}{d\varepsilon_2}$$

(22)

where  $\frac{dV_s}{d\varepsilon_2}$  can be obtained by (14), and its value is

$\frac{SR\tau_2}{a_1\varepsilon_2}$  . Then the average noise power of partial

slewing is

$$P_{par} = \int_{\varepsilon_{2} N_{S} = \frac{1}{a_{1}} SR \tau_{2}}^{\varepsilon_{2} N_{S} = \left(\tau_{2} + \frac{T}{2}\right) \frac{SR}{a_{1}}} f_{par}(\varepsilon) \cdot \varepsilon^{2} d\varepsilon$$

$$= \int_{V_{S} = \frac{SR \tau_{2}}{a_{1}}}^{V_{S} = \left(\tau_{2} + \frac{T}{2}\right) \frac{SR}{a_{1}}} f_{par}(V_{S}) \cdot \varepsilon_{2}^{2} dV_{S}$$

(23)

Finally, we analyze the settling noise in a fully slewing condition using the same procedure. First, if  $(\tau_2 + \frac{T}{2}) \frac{SR}{a_1} > 2V_{ref}$ , this condition will never occur. If  $(\tau_2 + \frac{T}{2}) \frac{SR}{a_1} < 2V_{ref}$ , then the fully slewing

probability is

$$Pr_{ful} = Erf\left[\frac{2V_{ref}}{\sigma_{VS}}\right] - Erf\left[\frac{SR(T + 2\tau_2)}{2\sqrt{2}a_1\sigma_{VS}}\right]$$

(24)

The pdf of  $V_s$  when  $|V_s| > (\tau_2 + \frac{T}{2}) \frac{SR}{a_1}$  is

$$f_{ful}(V_S) = \frac{1}{\Pr_{ful}} \cdot \frac{2}{\sqrt{2\pi} \cdot \sigma_{VS}} \exp(\frac{-V_S^2}{2 \cdot \sigma_{VS}^2})$$

(25)

The pdf of  $\varepsilon_2$  is

$$f_{ful}(\varepsilon_2) = f_{ful}(V_s) \cdot \frac{dV_s}{d\varepsilon_2}$$

(26)

So, the average noise power of fully slewing is  $P_{ful} = \int_{\varepsilon_2 | V_s = (\tau_2 + \frac{T}{2}) \frac{SR}{a_i}}^{\varepsilon_2 | V_s = (\tau_2 + \frac{T}{2}) \frac{SR}{a_i}} f_{ful}(\varepsilon) \cdot \varepsilon^2 d\varepsilon$

$$= \int_{V_S = \left(\tau_2 + \frac{T}{2}\right) \frac{SR}{a_1}}^{V_S = 2V_{ref}} f_{fill}(V_S) \cdot \varepsilon_2^2 dV_S$$

(27)

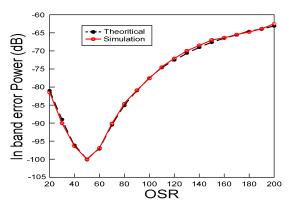

Fig. 8 Comparison of our theoretical result with behavior simulation result

The total average settling noise in the integration phase can be obtained by (18), (19), (20), (23), (24) and (27) as

$$P_{e_2} = \frac{P_{lin} \cdot \Pr_{lin} + P_{par} \cdot \Pr_{par} + P_{ful} \cdot \Pr_{ful}}{OSR}$$

(28)

In order to verify the result in (28), we use SIMULINK to build a second-order  $\Sigma\Delta$  modulator with a 4-bit quantizer. The behavioral settling model in [14] is used. We assume that  $a_1 = 0.5$ ,  $R = 300\Omega$ ,  $C_s = 1.7 \text{ pF}, GBW = 100 \text{ MHz}, f_B = 300 \text{ kHz} \text{ and}$  $SR = 100 \text{ V/}\mu\text{s}$ , and use a 300 kHz sinusoidal input signal. In an ideal behavior simulation with a sinusoidal input, the error  $\varepsilon_2$  can not be observed at modulator output, because  $\mathcal{E}_2$  is highly correlated with  $V_s$ , so that  $\mathcal{E}_2$  is compensated in the steady state by the integrator. However, adding a small noise to the input signal can eliminate the effects of feedback and integration. The theoretical noise power is obtained by adding the theoretical settling noise power from (28) to the theoretical quantization noise power. The simulated and theoretical noise powers are both shown in Fig. 8 vs. OSR. The two lines are closely related. When OSR < 50, quantization noise dominates. When OSR > 50, settling noise dominates. Notice that increasing SR and GBW will reduce settling noise and increase *SNR*, but will also increase analog power consumption and the design challenges.

In conclusion, if  $\varepsilon_2$  is independent of  $V_s$ , our settling noise model is correct and accurate. This model can be conservative if it is use in the design optimization discussed in Section III and IV, resulting in larger SR and GBW. However, the SR and GBW obtained from our design are still much smaller than those used in [5], as is discussed in Section IV. In addition, if we take into account the settling distortion issue (see Section IV and

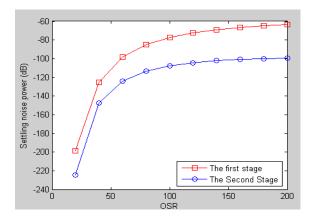

Fig. 9 Settling noise power for the first and the second stage integrators vs. *OSR*

Appendix A), this conservativeness may be indeed needed.

In integration phase, the settling error power for the second stage integrator is much smaller than that in the first stage, so generally it is not considered. This noise source appears at D2 in Fig. 10. The standard deviation of  $V_s$  for the second stage can be approximated by

$$\sigma_{VS} \approx \frac{1.06 \cdot \left| V_{ref} \right|}{2^B} \tag{29}$$

In general, the design specifications for the 1<sup>st</sup> and  $2^{nd}$  stage integrators are different, so the overall settling error power for the  $2^{nd}$  stage integrator  $P_{e_2\_2nd}(overall)$  can be obtain by substituting it's specifications into (16)~(27). Due to noise shaping, the total noise power in signal bandwidth is

$$P_{\varepsilon_{2}2nd} = \int_{-f_{in}}^{f_{in}} \frac{P_{\varepsilon_{2}2nd}(overall)}{f_{S}} \cdot 4Sin^{2} \left(\frac{f}{f_{S}}\pi\right) df \quad (30)$$

where  $4Sin^2 \left(\frac{f}{f_s}\pi\right)$  is the noise transfer function

for D2 [40]. The larger the *OSR*, the more effective noise shaping is. For the case that 1<sup>st</sup> and 2<sup>nd</sup> stage integrators are identical, Fig. 9 compares 1<sup>st</sup> and 2<sup>nd</sup> stage settling noise powers vs. *OSR*, which shows that the second-stage settling error is at least 22 to 36 dB less than that of the first stage.

#### 2.4 Multi-bit DAC noise

There are several advantages in using a multi-bit structure, which are discussed in [33, 34]. Due to CMOS process variations, there can be mismatches in the  $2^B$  unit capacitors  $C_\mu$  of a B-bit DAC shown

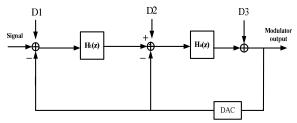

Fig. 10 Main nonidealities sources in the sigma delta modulator

in Fig. 4. Assume that each unit capacitor distribution is Gaussian [35] around a nominal value. Let the normalized capacitance be

$$c_{i} = \frac{C_{i}}{\sum_{k=1}^{2^{B}} C_{k}}, \quad 1 \le i \le 2^{B}$$

(31)

where  $C_i$  is the capacitance of the *i*th unit capacitor. Define the deviation of  $c_i$  as  $e_i = c_i - c_m$ , where

$$c_m = \frac{\sum_{i=1}^{2^B} c_i}{2^B}$$

(32)

Then voltage error caused by unit capacitor mismatches is given by [23]

$$e_{dac}(k) = V_{ref} \left( \sum_{i=1}^{x(k)} e_i - \sum_{i=x(k)+1}^{2^B} e_i \right)$$

(33)

where x(k) represents the number of 1's in the feedback thermometer code at the time step k. The

$e_{dac}(k)$  can be treated as an additive Gaussian noise in the  $\Sigma\Delta$  modulator feedback path, the variance of which is

$$\sigma^{2}[e_{dac}] = V_{ref}^{2}(x(k) \cdot \sigma^{2}[e_{i}] + (2^{B} - x(k)) \cdot \sigma^{2}[e_{i}])$$

$$= V_{ref}^{2} \cdot 2^{B} \cdot \sigma^{2}[e_{i}]$$

$$= V_{ref}^{2} \cdot 2^{B} \cdot \sigma_{cap}^{2}$$

(34)

where  $\sigma_{cap}$  is the standard deviation of unit capacitor. Assuming the  $e_{dac}(k)$  is also white, the average DAC noise power at the modulator output becomes

$$P_{dac} = \frac{1}{OSR} \cdot V_{ref}^{2} \cdot 2^{B} \cdot \sigma_{cap}^{2}$$

(35)

In order to reduce DAC error due to unit capacitor mismatch, several techniques have been proposed. The most efficient among these is the Data Weighted Averaging (DWA) [36], and it is shown in [37] that the DWA effect is a first-order noise shaping of the DAC noise. If the DWA is employed, the average DAC noise power at the modulator

output is modified to be

$$P_{dac}(DWA) \cong V_{ref}^{2} \cdot 2^{B} \cdot \sigma_{cap}^{2} \cdot \frac{\pi^{2}}{3 \cdot OSR^{3}}$$

(36)

Equations (33) and (34) will be used to estimate the DAC noise power in the optimization process.

#### 2.5 Clock Jitter Effects

As both the signal bandwidth and the required output SNR increase, clock jitter problems become more obvious. Jitter is usually defined as a random variation in clock signal period around the ideal value, and the value of jitter can be reasonably assumed as a Gaussian random variable with zero mean and standard deviation  $\sigma_{ji}$ . If there is some variation in clock high time, the input signal will be sampled at the wrong instant and receive a consequent voltage error. For a sinusoidal input signal with maximum amplitude  $A_{in}$  and frequency  $f_{in}$ , if it is sampled by a clock which has a jitter variation, then the voltage error is [2]

$$\Delta V \cong 2\pi \cdot f_{in} \cdot A_{in} \cos(2\pi \cdot f_{in} \cdot t) \Delta T \tag{37}$$

where  $\Delta T$  is the variation of clock period with standard deviation  $\sigma_{jit}$ . Then the jitter noise power becomes

$$P_{jitter} = \frac{(2\pi \cdot f_{in} \cdot A_{in})^2}{2} \cdot \frac{\sigma_{jit}^2}{OSR}$$

(38)

We consider the worst case in this work. That is,  $f_{in}$  and  $A_{in}$  are replaced by  $f_{B}$  and  $V_{ref}$  respectively.

More discussions about tolerable  $\sigma_{jit}$  will be given in the next section. We summarize the nonideality modeling as follows. The leakage noise due to finite OTA gain can be considered as an additional quantization noise, so the total quantization noise will be higher than theoretical quantization noise, appearing at D3 in Fig. 10. All other nonidealities in the first stage are modeled at D1 in Fig. 10, because we have modeled them as input-referred noise in the integrator input.

#### 2.6 Relative Power Model

In order to understand how  $\Sigma\Delta$  modulator power consumption is related to different circuit parameters, we must derive the power dissipation equation. Some derivations of this are based on the results presented in [23, 24, 25]. It is difficult to estimate real system level power consumption, so our goal is not to estimate the absolute value of the power, but to find how power changes with circuit parameters, it is called the relative power consumption. Typically,  $\Sigma \Delta$ **ADC** power consumption is categorized into analog and digital parts. The power dissipation in the quantizer is also considered. We analyze the analog part first. The analog power dissipation in a  $\Sigma\Delta$  modulator is mainly from OTA, and is proportional to the several of parameters:  $POW_{OTA} \sim k_{OTA} \cdot V_{DD} \cdot \pi \cdot C_{L2} \cdot GBW$ (39)

where  $k_{OTA}$  is the number of current branches of OTA and  $V_{DD}$  is the power supply. The  $k_{OTA}$  depends on the topology of OTA. The first integrator is the most important in terms of noise. Hence, all succeeding integrators are normally scaled down progressively to reduce the power consumption and die area. Consider that the sum of the relative scaling factors used in all the integrators of the  $\Sigma\Delta$  is  $k_{\Sigma\Delta}$ . Then the analog power

consumption equals  $k_{\Sigma\Delta} \cdot POW_{OTA}$ , where  $k_{\Sigma\Delta}$  is proportional to the order n of the  $\Sigma\Delta$  modulator. Assuming that the scaling factor is 0.5, then from (39), the total analog power consumption is :

$$POW_{analog} \cong k_{\Sigma\Delta} \cdot POW_{OTA}$$

$$\sim \left(\sum_{i=0}^{n-1} (0.5)^{i}\right) \cdot k_{OTA} \cdot V_{DD} \cdot \pi \cdot C_{L2} \cdot GBW \quad (40)$$

Since the analog power consumption is related to n,  $V_{DD}$ ,  $C_{L2}$  and GBW, they are important circuit parameters to be determined in the design flow. Next, we discuss digital power consumption. Digital power consumption is mainly from MOS switch operation, and is proportional to the product of another set of parameters:  $POW_{SW} \sim n \cdot 2^B \cdot C_{Switch} \cdot V_{DD}^2 \cdot 2 \cdot f_B \cdot OSR$  (41)

where  $2 \cdot f_B \cdot OSR$  is equal to the sampling frequency, and  $C_{Switch}$  is the total gate capacitance of switches. The value of  $C_{Switch}$  is inversely proportional to the switch-on resistance R [38], so we define the relative digital power as

$$POW_{digital} \sim n \cdot 2^{B} \cdot \frac{1}{P} \cdot V_{DD}^{2} \cdot f_{S}$$

(42)

Next we discuss quantizer power consumption. In the multi-bit ADC, a simple power estimation formula for Nyquist ADC [25] is

$$P_{quantizer} = \frac{V_{DD}^{2} \times L_{\min} \times (f_{s} + f_{b})}{10^{(-0.1525 \times B + 4.838)}}$$

(43)

where  $L_{\min}$  is the minimum channel length of the technology associated. According to the above discussion, the total relative power is defined as

$$Power = K_1 \times POW_{analog} + K_2 \times POW_{digital} + P_{quantizer}$$

(44)

where  $K_1$  and  $K_2$  are adjusted to make *Power* (in mW) comparable in magnitude with real power dissipations. After comparing with power measurements reported in [5, 11], we set  $K_1 = 0.03651$  and  $K_2 = 3.6877 \times 10^{-10}$ . Both [5] and [11] are based on 0.18-µm CMOS technology. For other CMOS technologies, the  $K_1$  and  $K_2$  may be set to other appropriate values.

Dynamic element matching (DEM) [36, 37, 47] is based on scrambling the use of the unit elements in

a multi-bit DAC to average out nonlinearity and turn distortion into noise. In general, the DEM logic grows exponentially in complexity, size, and power dissipation as the internal quantizer bit increases. And the power consumption of 120DEM depends on CMOS technology. Due to many possible variations in DEM designs, we do not try to calculate the power consumption for any specific type of DEM scheme. Instead, picking a medium value, we assume DEM power is  $0.6 \times Power$  if DEM is employed.

## 3 The Design optimization Scheme

Power and nonideality models derived in section II are employed to propose a design optimization algorithm, to search for optimal parameter combinations. Before the discussions, we formally define the peak SNR at  $\Sigma\Delta$  ADC output as

|                          | в↑ | osr∱ | n † | R∱ | GBW <sup>4</sup> | $C_s$ | SR∱ |

|--------------------------|----|------|-----|----|------------------|-------|-----|

| $P_{\mathcal{Q}}$ (1)    | 1  | 1    | +   | _  | _                | _     | 1   |

| $P_{AV}$ (1)             | 1  | 1    | +   | _  | _                | _     | _   |

| $P_{\varepsilon_1}$ (12) | 1  | 1    | _   | 1  | _                | 1     | _   |

| $P_{\varepsilon_2}$ (28) | +  | 1    | _   | _  | 1                | 1     | +   |

| $P_{dac}$ (35)           | 1  | 1    | _   | _  | _                | _     | 1   |

| $P_{jitter}$ (38)        | 1  | +    | _   | _  | -                | _     | 1   |

| $P_{sw}(2)$              | ı  | 1    | _   | _  | _                | 1     | I   |

| $P_{OTA}$ (6)            | _  | 1    | _   | _  | 1                | _     | -   |

| P <sub>ref</sub> (7)     | _  | 1    | _   | 1  | 1                | +     | _   |

| Power (44)               | 1  | 1    | 1   | 1  | 1                | 1     | 1   |

TABLE II Summary of noise-power and powerrating variations when design parameters increase

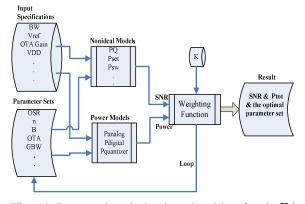

Fig. 11 Proposed optimization algorithm for the  $\Sigma\Delta$  modulator design

$$SNR = \frac{(2A_{in})^{2}/2}{P_{Q} + P_{AV} + P_{\varepsilon 1} + P_{\varepsilon 2} + P_{dac} + P_{jitter} + P_{sw} + P_{OTA} + P_{ref}}$$

(45)

Table II summarizes the facts from models in section II. Table II shows qualitatively how noise and power are affected when a particular design parameter increases, and it reveals that the  $\Sigma\Delta$  ADC design task is very complex. Basically we identify B, OSR, n, R, GBW,  $C_S$  and SR as the optimization process design parameters.

In the following we propose an design optimization algorithm to help designers reach an optimal design quickly. It is based on the error and power models described in section II. The complete flow of the optimization methodology is shown in Fig. 11. The input signal bandwidth (Hz) and the output signal SNR (dB) are treated as design specifications. We modify the figure-of-merit (FOM) [40] function by multiplying a variable *K* to the *SNR* term of FOM, to become our weighting function.

WF =

$$K \cdot SNR_{dB} + 10 \log \left( \frac{f_B}{Power} \right)$$

(46)

The design optimization algorithm basically searches through the entire parameter space to find the set of design parameters which maximize the Weighting Function. By maximizing the Weighting Function we can increase SNR (45) and reduce Power (44) at the same time.

The constant *K* serves as the relative weighting between *SNR* and *Power*. Typically, if we prefer high resolution designs, we set *K* higher and *SNR* plays a more important role than *Power*; on the other hand, if we prefer low power designs, we can set *K* lower. After an design optimization process, the set of design parameters resulting in the largest Weighting Function value is the outcome and is evaluated. If not acceptable, the *K* is adjusted and the design optimization process is repeated. The parameter searching space is specified to be

•  $OSR: 8 \sim 128$

•  $B: 1 \sim 6$  (if > 3, DEM is required)

• *n*:1~3

•  $R: 100 \Omega \sim 300 \Omega$

• *GBW*: 50 MHz ~ 500 MHz

•  $SR: 50 \frac{V}{\mu S} \sim 500 \frac{V}{\mu S}$

•  $C_s : 1 \text{ pF} \sim 10 \text{ pF}$

The parameters  $\sigma_{cap}$  and  $V_{ref}$  depend on the technology, so they are set before the design optimization. The tolerable value of jitter standard deviation  $\sigma_{jit}$  can be specified after the optimization

process. During the design optimization process, the gain coefficients  $a_i$  are specified according to the rules provided in [43].

## 4 Simulation Results

In order to demonstrate the accuracy and practicability of our method, we apply it to two published design cases [5, 28]. In addition, we compare our method with existing behavior-simulation-based optimization schemes [48, 49].

#### **4.1** $\Sigma\Delta$ **ADC** for **ADSL-CO** Applications

To compare with the design of [5], the design optimization algorithm uses the same specifications as those in [5]. They are:

• Peak *SNR* : 82 dB

• Signal bandwidth: 276 kHz

The OTA gain A is set at 60 dB and the  $V_{ref}$  is set at 0.9 V for a 1.8 V power supply in 0.18-µm CMOS technology. The matching of capacitor  $\sigma_{con}$ is set at 0.04% for the MIM capacitance. The results published in [5] and those obtained from our methodology are all listed in Table III, which three design optimization results corresponding to K=0.3, K=0.6, and K=0.7. From Table III, when K=0.6, the result of SNR = 83.3 dB satisfies the specification, although the Power = 3.7mW is higher than Power = 3.0 mW when K=0.3. The results from higher K are also reported. When K=0.7, the power consumption is dramatically larger at 26.2 mW, due to the fact that the DEM is employed and B is larger. We choose the case K=0.6(with SNR=83.3) as our design. The SNR generated from the SIMULINK behavior simulation is also included in Table III.

The design of [5] is also listed in Table III. The *SNR* and *Power* of [5] listed in Table III are computed from our models. The *SR* and *GBW* used in [5] are considerably larger than those of our design. According to Table VIII in the Appendix A, the values  $SR = 500 \frac{V}{\mu S}$  and GBW = 400 MHz are barely enough for OSR = 8, but are more than adequate for

OSR = 16. Since the OSR in [5] is designed to be 96, the SR and GBW values used in [5] are too large compared with the minimum required values at  $SR = 90 \frac{V}{\mu S}$  and GBW = 40 MHz listed in Table VIII, resulting in power consumption four times that of our design (15mW vs. 3.7mW). The SR and GBW in our design are adequate, with (SR, GBW) = (160, 90)

compared with the minimum required (110, 60) listed in Table VIII.

Table IV shows the corresponding noise powers for the four design cases shown in Table III. In the design of [5], and in our designs for K=0.6, the dominating noise power is  $P_{dac}$ . Our optimization process may help to distribute noise power more evenly among different noise categories, resulting in a larger gap between  $P_{dac}$  and  $P_{total}$ , where  $P_{total}$  is the sum of in band noise powers. The gap between  $P_{dac}$  and  $P_{total}$  from [5] is very small. Our optimization algorithm may also help designers consider less aggressive design parameters first, e.g., setting B = 2 instead of 3. When K=0.7, the optimization algorithm sets B to be 4, so the DEM technique is employed, and DAC noise is suppressed to -105.6 dB. Accordingly the  $P_{sw}$  at -95.6 dB becomes the dominating noise power. Finally, we want to report a case not listed in Tables

| circuit parameters          | in [5] | K=0.3 | K=0.6 | <i>K</i> =0.7 | Unit |

|-----------------------------|--------|-------|-------|---------------|------|

| OSR                         | 96     | 40    | 50    | 60            | -    |

| В                           | 3      | 2     | 2     | 4             | -    |

| n                           | 2      | 2     | 2     | 2             | -    |

| R                           | 300    | 300   | 300   | 300           | Ω    |

| $C_{s}$                     | 1.7    | 1     | 1     | 2             | pF   |

| $C_{\scriptscriptstyle L2}$ | 7.2    | 5.8   | 5.8   | 7.8           | pF   |

| GBW                         | 400    | 70    | 90    | 150           | MHz  |

| SR                          | 500    | 120   | 160   | 50            | V/µs |

| $\sigma_{_{jit}}$           | 15     | 15    | 15    | 15            | Ps   |

| SNR                         | 82.8   | 81.5  | 83.3  | 96.7          | dB   |

| <i>SNR</i> (SIMULINK)       | 82.3   | 80.8  | 83.1  | 95.5          | dB   |

| Power                       | 15     | 3.0   | 3.7   | 26.2          | mW   |

TABLE III Comparisons of our design results with those in [5]

| Noise                       | in [5]     | K = 0.3    | K =0.6     | K = 0.7    |

|-----------------------------|------------|------------|------------|------------|

| $P_Q$                       | - 109.8 dB | - 84.9 dB  | - 89.8 dB  | - 105.8 dB |

| $P_{\scriptscriptstyle AV}$ | -141.1dB   | - 123.6 dB | - 126.5 dB | - 141.0 dB |

| $P_{arepsilon 1}$           | - 196.5 dB | - 681.7 dB | - 551.5 dB | - 258.4 dB |

| $P_{arepsilon 2}$           | - 119.3dB  | - 103.9dB  | - 104.5dB  | - 120.0 dB |

| $P_{sw}$                    | - 96.9 dB  | - 90.8 dB  | - 91.8 dB  | - 95.6dB   |

| $P_{ref}$                   | - 114.7dB  | - 101.0dB  | - 103.1 dB | - 109.1 dB |

| $P_{OTA}$                   | - 117.0 dB | - 110.9 dB | - 111.9 dB | - 115.7 dB |

| $P_{dac}$                   | - 80.8dB   | -81.4dB    | - 82.3dB   | - 105.6dB  |

| $P_{total}$                 | - 80.7dB   | - 79.4 dB  | -81.2dB    | -94.6dB    |

TABLE IV The corresponding noise powers for the design parameters listed in Table III

|                 | Ref [5]              | K=0.3               | K=0.6                | K=0.7                 | Unit |

|-----------------|----------------------|---------------------|----------------------|-----------------------|------|

| $POW_{analog}$  | 64.6                 | 6.65                | 8.55                 | 28.5                  | -    |

| $POW_{digital}$ | 3.1×10 <sup>10</sup> | 6.4×10 <sup>9</sup> | 8.02×10 <sup>9</sup> | 3.85×10 <sup>10</sup> | -    |

| POWquantizer    | 1.29                 | 0.38                | 0.48                 | 1.15                  | mW   |

TABLE V List of the details of power consumption

III and IV. Suppose we change our rule to enable DEM when B is equal to or larger than 3. Then, for the case K=0.6, the algorithm sets B to be 3 (from 2),  $P_{dac}$  is reduced to -111.2 dB (from -82.3 dB), and SNR is raised to 97.2 dB (from 83.3 dB). But the power consumption is increased to 16.9 mW (from 3.7 mW).

Table V lists the power consumption details. From (38), we can see that the POW<sub>analog</sub> is proportional to the GBW and  $C_{L2}$ . The  $C_{L2}$  (16) is proportional to the sampling capacitance  $C_s$ . From Table III, we can see that the GBW of [5] is larger than that of K=0.3, K=0.6 and K=0.7 and  $C_s$  of [5] is larger than that of K = 0.3 and K = 0.6 (almost the same with K = 0.7). Hence, the  $POW_{analog}$  of [5] is the largest among the four cases. From (40), we can see that the  $POW_{digital}$  is proportional to the  $2^{B}$  and OSR. It is also inversely proportional to the onresistance R. The quantizer power  $POW_{output}$  (41) is related to OSR and B. The larger the OSR and B are, the larger the quantizer power *POW*<sub>quantizer</sub>. In Table III the *Power* of [5] is four times larger compared with that of K=0.6. This is due to the design of [5] employs larger GBW, OSR,  $C_s$ , and B, resulting in larger  $POW_{analog}$ ,  $POW_{digital}$  and  $POW_{quantizar}$ .

#### **4.2** ΣΔ **ADC** for Broadband Applications

To compare with the design of [28], the design optimization algorithm uses the same specifications as those in [28]. They are:

Peak *SNR*: 95 dB

Signal bandwidth: 1.25 MHz

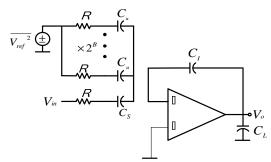

The DAC architecture in [28] (shown in Fig. 12) is different from the one shown in Fig. 1. Therefore, the noise powers  $P_{SW}$ ,  $P_{OTA}$  and  $P_{\varepsilon 1}$  must be modified, and the modifications are summarized in Appendix B. Other noise powers forms are the same as those in Sec. II, except that  $C_s$  is replaced by  $2^B \cdot C_u$ .

From TABLE VI, when K=1, SNR=96 dB satisfies the specification in [28]. Compared with the design in Case A, several points are worth mentioning. Although our GBW and SR in Case A are much smaller than the published ones [5], they are larger than the published ones [28] in Case B. This helps to avoid the impression that our method produces extreme results. Table IV shows that the dominating noise power in Case A is  $P_{dac}$ , while Table VII shows that in Case B the dominating power is  $P_{sw}$ . A reason is that the DEM is employed in Case B, but not in Case A.

# **4.3** Comparisons with Existing Optimization Schemes

Behavioral simulation based optimization strategy is popular for  $\Sigma\Delta$  ADC design [48, 49]. The comparisons between our method and general behavioral simulation methods are summarized as follows.

Fig. 12 The DAC architecture in [28]

| circuit parameters           | in [28] | K=0.3 | K=0.6 | K=1  | Unit |

|------------------------------|---------|-------|-------|------|------|

| OSR                          | 24      | 20    | 28    | 40   | -    |

| В                            | 4       | 3     | 3     | 3    | -    |

| n                            | 3       | 3     | 3     | 3    | -    |

| R                            | 220     | 300   | 300   | 200  | Ω    |

| $C_{\mu}$                    | 200     | 225   | 225   | 300  | fF   |

| $C_{_{L2}}$                  | 8.5     | 5     | 5     | 6.7  | pF   |

| GBW                          | 220     | 120   | 240   | 400  | MHz  |

| SR                           | 145     | 75    | 150   | 250  | V/µs |

| $oldsymbol{\sigma}_{_{jit}}$ | 9       | 9     | 9     | 9    | Ps   |

| SNR                          | 94.1    | 89.7  | 94.5  | 98   | dB   |

| SNR(SIMULINK)                | 94.6    | 90.3  | 95.8  | 99.1 | dB   |

| Power                        | 300     | 118   | 167   | 303  | mW   |

TABLE VI Comparisons of our design results with those in [28]

|                   | Ref [5]              | K=0.3   | K=0.6                | K=0.7                 | Unit |

|-------------------|----------------------|---------|----------------------|-----------------------|------|

| $POW_{analog}$    | 64.6                 | 6.65    | 8.55                 | 28.5                  | -    |

| $POW_{digital}$   | 3.1×10 <sup>10</sup> | 6.4×10° | 8.02×10 <sup>9</sup> | 3.85×10 <sup>10</sup> | -    |

| $POW_{quantizer}$ | 1.29                 | 0.38    | 0.48                 | 1.15                  | mW   |

TABLE VII List of the details of power consumption

- 1.Pentium D, 2.8GHz CPU). To make a fair comparison, both methods are implemented under Matlab-Simulink environment. For our approach, the SNR in (45) is computed by a Matlab program (originally implemented in *Mathmatica*). The CPU time is 62.5 ms. For behavior simulation approach, a 16384 point simulation is run under Simulink, and the total CPU time is 13.01 seconds, Our method is 208.2 times faster.

- 2. The optimization result from behavior simulations provides only the total noise power, while our method can generate each individual noise power as is listed in Table IV and Table VII, which provides greater insights and can serve several practical purposes. For example, suppose the design objective is not met even after the optimization process. The simulation approach might shed little clue about how things can be tackled. On the other hand, our result would indicate which noise power is the dominating one, and a different technology can be adopted to reduce that particular noise.

- 3. The disadvantage of our method is low flexibility, because equations may be modified every time when the topology is changed. In contrast, it is generally straightforward to simulate various  $\Sigma\Delta$  modulator architectures by properly linking building blocks into appropriate forms.

#### 5 Conclusion

The main contributions of this work are described in the following. First, a settling error model of the switched capacitor integrators in  $\Sigma\Delta$  modulators is constructed using statistical analysis. This model considers settling errors in both the sampling and integration phases, represented in noise-power form. We also derive the DAC noise-power model. Additionally, we make modifications to existing noise-power models of other noises, particularly to thermal noise models. The noise-power models of all major noises and errors are established in Section II, and the SNR is defined in (45) accordingly. Second, based on nonideality models and the

relative power model, we propose an optimization algorithm in Section III. In contrast to the complexity and difficulty encountered in the conventional  $\Sigma\Delta$  modulator design approach, this algorithm can completely and efficiently search the entire design parameters space to find the parameter set which satisfies the specifications, while achieving the lowest power consumption. Third, the complete models allow for analytical evaluation of design results, whether they are generated from our algorithm or designed elsewhere. For example, information provided in Table IV and V can reveal which noise or power is the dominating factor. Then, the models in Section II can help find design parameters behind the dominating factor. Fourth, our optimization method can be hundreds of times faster than existing behavioral simulation based approaches.

This paper works on optimization of SNR, not SNDR. For radio and communication applications, maximize SNDR becomes an important issue. We are currently working on creating a complete set of nonlinear distortion models, so that SNDR optimization can be realized.

## **APPENDIX**

## A: Settling Distortion Model

In a  $\Sigma\Delta$  modulator, nonlinear distortions can be categorized into op-amp gain nonlinearity distortion [18, 23, 46], settling distortion [18, 42, 46], nonlinear capacitances distortion [18, 23], quantizer nonlinearity distortion [34], nonlinear switch resistance distortion [23, 32] and DAC distortion [34, 37, 44, 45]. It can be verified that settling distortion is the sole distortion which can be significantly affected by op-amp slew rate (SR) and gain-bandwidth (GBW). There was a great effort in [46] to model settling distortion. However the result in [46] reached a wrong conclusion, and it showed little insight about how SR and GBW are quantitatively related to settling distortion. In this appendix, we provide a comprehensive model for settling distortion. This model is used in section IV to explain why the SR and GBW in [5] are too large, but the SR and GBW obtained in our design are adequate.

Consider the integrator operates in the integration phase. As discussed in section II, there are three settling conditions depending on the absolute value of  $V_s$ .

1. Linear settling

$$\left( |V_s| < \frac{1}{a_1} \cdot SR \cdot \tau_2 \right)$$

:

We can represent integrator output voltage during the *n*th integration interval as

$$\begin{split} V_o(t) = & V_o(nT-T) + a_1 V_S(1 - e^{\frac{-(t-nT + \frac{T}{2})}{\tau_2}}), \\ & nT - \frac{T}{2} < t < nT \end{split} \tag{47}$$

2. Partial slewing

$$\left(\frac{1}{a_1} \cdot SR \cdot \tau_2 < |V_S|\right)$$

:

$$V_o(t) = V_o(nT - T) + SR \cdot (t_0 - nT + \frac{T}{2})$$

$$+ \left[a_1 V_S - SR \cdot (t_0 - nT + \frac{T}{2})\right] (1 - e^{\frac{-(t - t_0)}{\tau_2}}), \quad t > t_0$$

(48)

where  $t_0$  is the time instant when  $V_o$  rate becomes less than SR. The full slewing case is not considered here because it is not significant. Note that (47) and (48) at end of each integration interval can be rewritten as

$$V_o(nT) = V_o(nT - T) + a_1 V_S(1 - e^{-\left(\frac{T}{2\tau_2} + 1\right)} \cdot e)$$

$$= V_{o}(nT - T) + a_{1}V_{S}(1 - \beta \cdot e) , \quad |V_{S}| \le V_{L}$$

$$V_{o}(nT) = V_{o}(nT - T) + a_{1}V_{S} \left[ 1 - \frac{SR\tau_{2}}{a_{1}V_{S}} \cdot e^{-\left(\frac{T}{2\tau_{2}} - \frac{a_{1}|V_{S}|+1}{SR\tau_{2}}\right)} \right]$$

$$= V_{o}(nT - T) + a_{1}V_{S} \left[ 1 - \frac{V_{L}}{V_{S}} \cdot \beta e^{|V_{S}|/V_{L}} \right], |V_{S}| > V_{L}$$

$$(49)$$

where  $\beta = e^{-(T/(2\tau_2)+1)}$  and  $V_1 = SR\tau_2/a_1$ .

Let

$$g_{i}(V_{s}) = \begin{cases} a_{1}(1 - \beta e) ; & |V_{s}| \leq V_{L} \\ a_{1}(1 - \frac{V_{L}}{V_{s}} \beta e^{|V_{s}|/V_{L}}) ; |V_{s}| > V_{L} \end{cases}$$

(50)

which is the integrator gain. Assume that  $g_i(v)$  can be approximated by

$$p(v) = a_1 \cdot (\alpha_1 + \alpha_2 v^2 + \alpha_5 v^4) \tag{51}$$

We use the least square method to determine the coefficients  $\alpha_1$ ,  $\alpha_3$  and  $\alpha_5$  such that the cost function

$$q = \sum_{i=1}^{n} [g_i(x_j) - p(x_j)]^2$$

$$= \sum_{i=1}^{n} \left[ g_i(x_j) - a_1 \alpha_1 - a_1 \alpha_3 x_j^2 - a_1 \alpha_5 x_j^4 \right]^2$$

(52)

is minimized over a specific interval, and the solution is found to be

$$\begin{bmatrix} \alpha_{l} \\ \alpha_{s} \\ \alpha_{s} \end{bmatrix} = \begin{bmatrix} \frac{225}{64V_{h}} & \frac{-525}{32V_{h}^{3}} & \frac{945}{64V_{h}^{5}} \\ \frac{-525}{32V_{h}^{3}} & \frac{2205}{16V_{h}^{5}} & \frac{-4725}{32V_{h}^{7}} \\ \frac{945}{64V_{h}^{5}} & \frac{-4725}{32V_{h}^{7}} & \frac{11025}{64V_{h}^{5}} \end{bmatrix} \int_{0}^{V_{L}} (1-\beta e) \cdot V_{S}^{2} dV_{S} + \int_{V_{L}}^{V_{h}} (1-\frac{V_{L}}{V_{S}} \beta e^{|V_{S}|/V_{L}}) V_{S}^{2} dV_{S} \\ \frac{945}{64V_{h}^{5}} & \frac{-4725}{32V_{h}^{7}} & \frac{11025}{64V_{h}^{5}} \end{bmatrix} \int_{0}^{V_{L}} (1-\beta e) \cdot V_{S}^{4} dV_{S} + \int_{V_{L}}^{V_{h}} (1-\frac{V_{L}}{V_{S}} \beta e^{|V_{S}|/V_{L}}) V_{S}^{4} dV_{S} \end{bmatrix}$$

$$(53)$$

where  $V_h$  is the distribution range of the first integrator input  $V_s$ . The amplitudes of the third and fifth harmonics

of the modulator output are:

$$A_{3} \cong \frac{|\alpha_{3}|A_{vs}^{3}}{4} \quad ; \quad A_{5} \cong \frac{|\alpha_{5}|A_{vs}^{5}}{16} \qquad (54)$$

where  $A_{vs}$  is the amplitude of  $V_s$ . However, in [46],  $A_{in}$  instead of  $A_{vs}$  is employed in (54), where  $A_{in}$  is the amplitude of a sinusoidal modulator input signal. It is intuitively clear that using  $A_{in}$  is not correct, and our simulation shows that (54) is correct and precise. Next we are to obtain an expression for  $A_{vs}$ .

$$V_{s}(z) = X(z) - Y(z) \tag{55}$$

In a second-order  $\Sigma\Delta$  modulator, modulator output signal Y(z) is the time delay version of X(z) plus

high-pass filtered (noise shaped) quantization noise E(z). Therefore,

$$Y(z) = z^{-2}X(z) + (1 - z^{-1})^{2}E(z)$$

(56)

Combining (55) and (56),  $V_s(z)$  can be written as

$$V_c(z) = X(z)[1 - z^{-2}] - (1 - z^{-1})^2 E(z)$$

(57)

Ignoring the quantization noise and taking the inverse z-transform, one obtains

$$V_s(t) = x(t) - x(t - 2T)u(t - 2T)$$

$$= A_{in} \sin(\omega t) - A_{in} \sin(\omega (t - 2T)) \cdot u(t - 2T)$$

(58)

Then, the amplitude of  $V_s$  can be obtained as

$$A_{VS} = V_S(2T) = A_{in} \sin(\omega \cdot 2T) \cong 2A_{in} \cdot \omega \cdot T$$

(59)

Note that  $A_{vs}$  is not related to quantizer bit number B which can only affect the level of noise floor  $E(\omega)$ . The result (59) has been verified by behavior simulation under different B values.

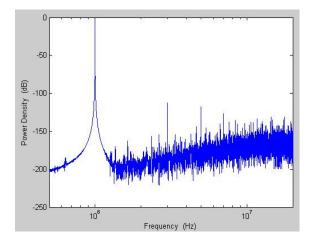

In order to verify the result in (54), we use SIMULINK to build a second-order  $\Sigma\Delta$  modulator with a multi-bit quantizer. The behavioral settling model in [14] is employed. We assume that  $SR=70 \frac{V}{\mu S}$ , GBW=100 MHz,  $R=300 \Omega$ , OSR=16,  $f_B=1 \text{MHz}$  and  $C_S=2 \text{pF}$ , and a 1MHz sinusoidal input signal is used. After performing FFT to the output data of the  $\Sigma\Delta$  modulator, we obtain the simulated PSD (Power Spectrum Density) which is shown in Fig. 13. It shows that HD3 is -112.5dB and HD5 is -117.5dB. The theoretical harmonic powers calculated from (53) and (54) are HD3 = -112.4dB and HD5 = -117.3dB. The simulated and theoretical results are very close, and this confirms

Fig. 13 Output spectrum of a second-order sigmadelta modulator with harmonic distortion

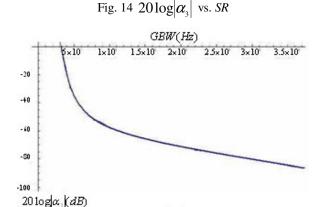

Fig. 15  $20\log|\alpha_3|$  vs. *GBW*

that our settling distortion model is reasonably precise.

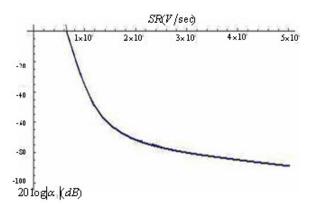

In order to provide insight on how settling distortions are related to circuit and system parameters, we further analyze the 3<sup>rd</sup> and 5<sup>th</sup> harmonic powers as follows:

| OSR | HD3(dB)                 | SR<br>(V / μs) | GBW<br>(MHz) |

|-----|-------------------------|----------------|--------------|

| 8   | $20\log  \alpha_3 $ -24 | ≥ 500          | ≥ 380        |

| 16  | $20\log  \alpha_3 $ -42 | ≥ 200          | ≥ 180        |

| 32  | $20\log  \alpha_3 $ -60 | ≥120           | ≥ 70         |

| 50  | $20\log \alpha_3 $ -72  | ≥110           | ≥ 60         |

| 64  | $20\log \alpha_3 $ -78  | ≥ 100          | ≥ 50         |

| 96  | $20\log  \alpha_3 $ -89 | ≥ 90           | ≥ 40         |

Table VII Minimum SR and GBW required w.r.t. OSR

$$HD3(dB) = 20\log\left(\frac{1}{\sqrt{2}} \left(\frac{|\alpha_{3}| A_{vs}^{3}}{4}\right)\right)$$

$$= 20\log|\alpha_{3}| - 60\log OSR + 30.095 \qquad (60)$$

$HD5(dB) = 20\log|\alpha_s| - 100\log OSR + 48.15$

From (60) we can see that *OSR* can effectively influence settling harmonic powers. The (53) reveals that  $\alpha_3$  and  $\alpha_s$  are functions of *T*, *GBW*, *R*,  $C_s$  and *SR*. Using the parameters designed in Section IV with  $f_s = 50$ MHz, R = 300ohm,  $C_s = 2$ pF, and setting *GBW* and *SR* at *GBW* = 250MHz and SR = 2

In general, harmonic distortion less than -110dB can be ignored because it is below the noise floor of modulator output spectrum. From (60), Fig. 14 and Fig. 15, we can obtain the minimum required *SR* and *GBW* w.r.t. a specific *OSR*. The results are summarized in Table VIII. It is clear from Table VIII that as *OSR* decreases, *SR* and *GBW* have to increase dramatically so that the effect of settling distortion can be contained. This can be explained by (59), since *T* increases when *OSR* decreases.

## APPENDIX B

For Case B in Section IV, the  $P_{\varepsilon 1}$ ,  $P_{sw}$  and  $P_{OTA}$  are modified as follows.

1. P.

The total charge transmitted to all unit capacitors  $C_{u}$  in sampling phase is

$$Q = N_{p} \cdot [V_{in+} - (V_{in+} - V_{r}) \cdot e^{(-\frac{T}{2RC_{u}})}] \cdot C_{u}$$

$$+ N_{n} \cdot [V_{in+} - (V_{in+} + V_{r}) \cdot e^{(-\frac{T}{2RC_{u}})}] \cdot C_{u}$$

(61)

where  $N_p$  and  $N_n$  represents the number of unit capacitors connected to  $V_r$  and  $-V_r$  respectively, and  $N_p + N_n = 2^B$ . The (61) can be simplified to

$$Q = [V_{int} + V_s \cdot e^{(-\frac{T}{2R \cdot C_u})}] \cdot 2^B \cdot C_u$$

(62)

where  $V_s = \frac{(N_P - N_n)}{2^B} \cdot V_r - V_{in+}$ , so the settling error during the sampling phase is  $\varepsilon_1 = V_S \cdot e^{(-\frac{T}{2RC_u})}$ . The noise power can be easily derived as:

$$P_{\varepsilon 1} = \frac{1}{OSR} \cdot \left(\frac{1.4 \cdot V_{\text{ref}}}{2^{B}}\right)^{2} \cdot e^{\left(-\frac{T}{2 \cdot R \cdot C_{u}}\right)} \quad (63)$$

Since  $C_u$  is much smaller than  $C_s$ , the settling error during the sampling phase in (61) is much smaller than

that in (12). If B is high enough,  $P_{\varepsilon 1}$  can even be neglected.

The integrator and the feedback DAC are combined by splitting up  $C_s$  in [5] into  $2^B$  parallel unity capacitors  $C_u$ , so the KT/C noise from input branch in Fig.1 can be excluded, and the total noise power become half that of (2), which is:

$$P_{sw} \cong \frac{1}{OSR} \cdot \left(\frac{4kT}{C_S}\right) \tag{64}$$

Here an assumption for (62) is  $C_S = 2^B \cdot C_u$ .

3.  $P_{OTA}$

Equation (4) is modified to become

$$\frac{\mathbf{V}_{\mathrm{O}}}{\mathbf{V}_{\mathrm{no}}}(s) \cong \begin{pmatrix} \frac{a_{1} + 1 + sC_{u}R}{1 + sC_{u}R} \end{pmatrix} \begin{pmatrix} 1 + \frac{s}{GBW/A} \end{pmatrix}$$

$$(65)$$

The noise power still can be obtained from (6), with (4) replaced by (65).

#### References:

- [1] E. Fogleman, I. Galton, W. Huff and H. Jensen, "A 3.3-V Single-Poly CMOS Audio ADC Delta-Sigma Modulator with 98-dB Peak SINAD and 105-dB Peak SFDR," *IEEE J. Solid-State Circuits*, vol. 35, pp. 297-307, March 2000.

- [2] B. E. Boser and B. A. Wooley, "The Design of Sigma-Delta Modulation Analog-to-Digital Converters", *IEEE J. Solid-State Circuits*, vol. 23, pp. 1298-1308, Dec. 1988.

- [3] S. R. Norsworthy, I. G. Post and H. S. Fetterman, "A 14-bit 80-kHz Sigma-Delta A/D Converter: Modeling, Design, and Performance Evaluation," *IEEE J. Solid-State Circuits*, vol. 24, pp. 256-266, April. 1989.

- [4] <a href="http://www.dspg.com/dspg/codec.html">http://www.dspg.com/dspg/codec.html</a>

- [5] R. Gaggl, A. Wiesbauer, G. Fritz, C. Schranze, P. Pessel, "A 85-dB Dynamic Range Multibit Delta-Sigma ADC for ADSL-CO Applications in 0.18-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 38, pp. 1105-1114, Jul. 2003.

- [6] R. d. Rio, J. M. Rosa, B. P. Verdu....., "Highly Linear 2.5-V CMOS ΣΔ Modulator for ADSL+," *IEEE Trans. on Circuits and Syst. I*, vol. 51, pp. 47–62, Jan. 2004.

- [7] O. Oliaei, P. Clément and P. Gorisse, "A 5-mW Sigma–Delta Modulator with 84-dB Dynamic Range for GSM/EDGE," *IEEE J. Solid-State Circuits*, vol. 37, pp. 2-10, Jan. 2002.

- [8] R. Gaggl, A. Wiesbauer, G. Fritz, C. Schranze, P. Pessel, "A 85-dB Dynamic Range Multibit Delta-Sigma ADC for ADSL-CO Applications in 0.18-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 38, pp. 1105-1114, Jul. 2003.

- [9] R. d. Rio, J. M. Rosa, B. P. Verdu....., "Highly Linear 2.5-V CMOS ΣΔ Modulator for ADSL+," *IEEE Trans. on Circuits and Syst. I*, vol. 51, pp. 47–62, Jan. 2004.

- [10] J. Grilo, I. Galton, K. Wang and G. Montemayor, "A 12-mW ADC Delta-Sigma Modulator With 80dB of Dynamic Range Integrated in a Single-Chip Bluetooth Transceiver," *IEEE J. Solid-State Circuits*, vol. 37, pp. 271-278, March 2002.

- [11] R. Miller and S. Petrie, "A Multibit Sigma-Delta ADC for Multimode Receivers," *IEEE J. Solid-State Circuits*, vol. 38, pp. 475-482, March 2003.

- [12] L. Yao, M. Steyaert and W. Sansen, "A 1-V 140-uW 88-dB Audio Sigma-Delta Modulator in 90-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 39, pp. 1809-1818, Nov. 2004.

- [13] K. Francken, P. Vancorenland, and G. Gielen, "DAISY: A simulation-based high-level synthesis tool for delta-sigma modulators," in *Proc. IEEE/ACM Int. Conf. Computer-Aided Design*, pp.188–192, Nov. 2000.

- [14] P. Malcovati, S. Brigati, F. Francesconi, F. Maloberti, P. Cusinato and A. Baschirotto, "Behavioral modeling of switched-capacitor sigma-delta modulators," *IEEE Trans. on Circuits and Syst. I*, vol. 50, pp. 352-364, Mar. 2003.

- [15] J. Y. Wu, S. B. Bibyk, "An efficient model for delta-sigma modulators," *Circuits and Systems,* 2001. MWSCAS 2001. Proceedings of the 44th IEEE 2001 Midwest Symposium, pp. 227 230, vol. 1, Aug. 2001.

- [16] S. M. Kashmiri, H. Hedayati, "Behavioral Modeling to circuit design steps of a 3-V digital audio sigma-delta modulator in 0.35um-CMOS," *Electrical and Computer Engineering*, 2003. *IEEE CCECE* 2003. Canadian Conference, vol.1, pp. 89 92.

- [17] V. F. Dias, G. Palmisano, P.O'Leary, F. Maloberti, "Fundamental Limitations of Switched-Capacitor Sigma-Delta Modulators," *IEEE Proceedings-G*, Vol. 139, pp. 27-32, Feb. 1992.

- [18] F. Medeiro, A. P. Verdu, A. R. Vazquez, *Top-Down Design of High Performance Sigma-Delta Modulators*, Kluwer academic publishers, 1999.

- [19] I. Marocco, "A noise model platform for discrete-time sigma-delta A/D converters in VLSI design," Diploma Thesis, Politecnico di Bari, Bari, Italy, 2000.

- [20] M. Terrovitis, K. Kundert, "Device noise simulation of  $\Delta\Sigma$  modulators," 2003. In www.designers-guide.com.

- [21] J. Grilo, I. Galton, K. Wang and G. Montemayor, "A 12-mW ADC Delta-Sigma Modulator With 80dB of Dynamic Range Integrated in a Single-Chip Bluetooth Transceiver," *IEEE J. Solid-State Circuits*, vol. 37, pp. 271-278, March 2002.

- [22] R. Schreier, M. Goodson and B. Zhang, "An algorithm for computing convex positively invariant sets for delta-sigma modulators," *IEEE Trans. on Circuits and Syst. I*, vol. 44, pp. 38–44, Jan. 1997.

- [23] Y. Geerts, M. Steyaert and W. Sansen, *Design* of *Multi-bit Delta-Sigma A/D Converters*, Kluwer Academic Publishers, Inc., 2002.

- [24] A. Marques, V. Peluso, M. Steyaert and W. Sansen, "Analysis of the Trade-off between Bandwidth, Resolution and Power in  $\Delta\Sigma$  Analog to Digital Converters," *Proceedings IEEE International Symposium on Circuits and Systems*, Atlanta, pp. 153-156, May 1998.

- [25] E. Lauwers and G. Gielen, "Power Estimation Methods for Analog Circuits for Architectural Exploration of Integrated Systems, " *IEEE Trans. on VLSI systems*, vol. 10, pp. 155-162, Apr 2002.

- [26] Paul R.Gray, Paul J.Hurst, Stephen H.Lewis and Robert G.Meyer, *Analysis and design of analog integrated circuits*, John Wiley & Sons, Inc., 2001.

- [27] B. Razavi, *Design of Analog CMOS Integrated Circuit*, McGraw-Hill series in electrical and Computer engineering, McGraw-Hill, 2001.

- [28] Y. Geerts, M. Steyaert and W. Sansen, "A High-Performance MultiBit ΔΣ CMOS ADC," *IEEE J. Solid-State Circuits*, vol. 35, pp. 1829–1840, Dec. 2000.

- [29] T. Piessens, M. Steyaert and E. Bach, "A Difference Reference Voltage Buffer for Delta Sigma-Converters," *Analog Integrated Circuits and Signal Processing*, Kluwer Academic Publishers, Vol. 31, pp. 31-37, 2002.

- [30] R. del Rio, F. Medeiro, B. Perez-Verdu, and A. Rodriguez-Vazquez, "Reliable Analysis of Settling errors in SC Integrators-Application to the Design of High-speed ΣΔ Modulators," Proceedings ISCAS 2000 Geneva. The 2000 IEEE International Symposium, vol. 4, pp. 417-420, May 2000.

- [31] S. Rabii and B. A. Wooley, *THE DESIGN OF LOW-VOLTAGE*, *LOW-POWER SIGMA-DELTA MODULATORS*, KLUWER ACADEMIC PUBLISHERS, 1999.

- [32] Y. Geerts, A.M. Marques, M.S.J. Steyaert and W. Sansen "A 3.3-V, 15-bit, Delta-Sigma ADC with a Signal Bandwidth of 1.1MHz for ADSL Applications" *IEEE J. Solid-State Circuits*, vol. 34, pp. 927-936, July 1999.

- [33] P. J. Hurst, R. A. Levinson and D, J, Block, "A Switched-Capacitor Delta-Sigma Modulator with Reduced Sensitivity to Op-Amp Gain," *IEEE J. Solid-State Circuits*, vol. 28, pp. 691–696, June 1993.

- [34] S. R. Norsworthy, R. Schreier, and G. C. Temes, Delta-Sigma Data Converters-Theory, Design and Simulation, IEEE Press, New Jersy, 1997.

- [35] M. J. M. Pelgrom, A. C. J. Duinmaijer and A. P. G. Welbers, "Matching Properties of MOS Transistors," *IEEE J. Solid-State Circuits*, vol. 24, pp. 1433–1439, Oct. 1989.

- [36] R. T. Baird and T. S. Fiez, "Linearity enhancement of multi-bit A/D and D/A converters using data weighted averaging," *IEEE Trans. on Circuits and Syst. II*, vol. 42, pp. 753–762, Dec. 1995.

- [37] J. A. P. Nys and R. K. Henderson, "An Analysis of Dynamic Element Matching Techniques in Sigma-Delta Modulation," *Proceedings IEEE International Symposium on Circuits and Systems*, Atlanta, pp. 231-234, May 1996.

- [38] N. H. E. Weste, K. Eshraghian, *PRICIPLES OF CMOS VLSI DESIGN*, A Systems Perspective, second edition, Addison-Wesley Press, 1994.

- [39] P. E. Allen, D. R. Holberg, *CMOS Analog Circuit Design*, second edition, OXFORD UNIVERSITY PRESS, 2002.

- [40] R. Schreier and G. C. Temes, Understanding Delta-Sigma Data Converters, IEEE Press, A JOHN WILEY & SONS, INC. Publication, 2005.

- [41] A. Marques, V. Peluso, M. S. Steyaert, and W. M. Sansen, "Optimal parameters for ΔΣ modulator topologies," *IEEE Trans. on Circuits and Syst. II*, vol. 45, pp. 1232–1241, Sept. 1998.

- [42] W. Sansen, Q. Huang and K. Halonen "Transient analysis of charge transfer in SC filter," *IEEE Journal of Solid-State Circuits*, sc-22(2):268-276, 1987.

- [43] V. F. Dias, G. Palmisano and F. Maloberti, "Harmonic Distortion in SC Sigma-Delta Modulators," *IEEE Trans. on Circuit and Systems*, vol. 41, NO.4, April 1994.

- [44] J. W. Bruce and P. Stubberud, "An Analysis of Harmonic Distortion and Integral Nonlinearity

- in Digital to Analog Converters," *IEEE Trans. on Circuit and Systems*, vol. 1, pp. 470-473, Aug. 1999.

- [45] P.Stubberud and J. W. Bruce, "An Analysis of Dynamic Element Matching Flash Digital-to-Analog Converters," *IEEE Trans. on Circuit and Systems*, vol. 48, pp. 205-213, Feb. 2001.

- [46] F. Medeiro, B. Perez-Verdu, A. Rodriguez-Vazquez and J. L. Huertas, "Modeling OpAmp-Induced Harmonic Distortion for Switched-Capacitor sigma-delta Modulator Design," in Proceedings of IEEE ISCAS, vol. 5, pp. 445-448, 1994

- [47] T. H. Kuo, K. D. Chen and H. R. Yeng, "A Wideband CMOS Sigma-Delta Modulator With Incremental Data Weighted Averaging," *IEEE J. Solid-State Circuits*, vol. 42, pp. 753-762, Dec. 1995.

- [48] K. Franchen and G. G. E. Gielen, "A High-Level Simulation and Synthesis Environment for ΣΔ Modulators," *IEEE Trans. Comput. Aided Des. Integr. Circuit Syst.*, vol. 22, no 8, pp. 1049-1061, Aug. 2003.

- [49] J. Ruiz-Amaya, J. M. de la Rosa, F. V. Fernandez, F. Medeiro, R. del Rio, B. Perez-Verdu, and A. Rodriguez-Vazquez, "High-Level Synthesis of Switched-Capacitor, Switched-Current and Continuous-Time ΣΔ Modulators Using SIMULINK-Based Time-Domain Behavioral Models," *IEEE Trans. on Circuit and Systems*, vol. 52, no. 9, pp. 1795-1810, Sep. 2005.

- [50] C. C. Enz and G. C. Temes, "Circuit Techniques for Reducing the Effect of Op-Amp Imperfections: Autozeroing, Correlated, Double Sampling, and Chopper Stabilization," *Proceedings IEEE*, vol. 84, pp. 1584-1614, Nov. 1996.

- [51] Adam Charles Thompson, Zahir M. Hussain, and Peter O'Shea, "A Correlative Criterion for the Stability of Sigma-Delta Based IIR Filter: Application to an FIR-like Bit-Stream Filter" ELECTRONICS, CONTROL and SIGNAL PROCESSING (ICECS '03), DECEMBER 7, 2003

- [52] Sau-Mou Wu, Rou-Yi Liu, Chia-Hau Chang, and Chao-Chyun Chen, "A 4th-Order Bandpass Sigma-Delta Modulator" of the WSEAS Multiconference: Signal Processing, Robotics and Automation (ISPRA '02)Microwaves, Antennas and Radar Systems (IMARS '02)Electronics and Hardware Systems (IEHS'02), Andalucia Beach, Chiclana, Cadiz, Spain, pp. 1371-1374, June 12-16, 2002.

[53] Ehsanollah Fathi, "A 3-V Digital-Audio Sigma-Delta Modulator in 0.35-μm CMOS" ELECTRONICS, CONTROL and SIGNAL PROCESSING (ICECS '03) , DECEMBER 7, 2003