## Analog adaptive filter LMS algorithm using CMOS 0.5 µm technology

Jose E. Perez-Carmona, Hector M. Perez-Meana and Juan C. Sanchez-Garcia Research and Graduate School Superior School of Mechanical and Electric Engineering ESIME IPN Av. Santa Ana No 1000, Col. San Francisco Culhuacan México D.F. Perese 013@yahoo.com.mx, hmpm@prodigy.net.mx, jcsanchezgarcia@gmail.com

Abstract: In this paper an analog adaptive filter circuit is presented, their coefficients are adapted with analog LMS algorithm using CMOS HP 0.5um technology. The layout simulation result shows fast convergence speed and low power consumption. The performance in configuration as an identifier shows that this circuit can be used in portables VLSI communications systems.

Keywords: Adaptive filters, LMS identifier, Analog CMOS circuits, Analog building blocks, Analog processing

## **1** Introduction

In the last decade the interest for the adaptive analog processing has been increasing in such a way that it is considered greatly as a research subject for the present time. This is due to the advance within the design technologies VLSI that has made possible the development of adaptive analog filter structures that have the capability to handle in real time signals of high frequency, and also implies major convergence velocities, less energy consumption and a small integration and linearity area [1].

These factors make the adaptive analog filters an attractive alternative in respect to the digital ones in practical applications such is the case of the equalization or matching of mobile terrestrial communication channels, echo suppressors etc.

The majority of the adaptive analog filters that have been proposed in literature, use the continuous time version of the algorithm of minimum square percentage (LMS), with a constant convergence factor to actualize the vector of the filter coefficients [2] and that should be maintained small enough to avoid the degradation of the convergence due to the fluctuation of the power of the input signal. The adaptive analog filters present several problems, mainly because of the realization limiting of some circuits in VLSI, for example the analog integration circuits that may degrade considerably the yield or efficiency of the global system. This block is fundamental in the LMS algorithm since it is the one that actualizes the coefficients of the filter; if this block is not properly designed the efficiency of the filter diminishes substantially. In many cases, the integrator circuit may be approximated by a low-pass filter with a cutoff frequency less than the minimum of the frequencies that conform the signal that is processed, that is, as close to zero as it is possible for any signal.

This condition is hard to satisfy in many of the practical applications, encouraging a degradation of the adaptive filter behavior, since a cut frequency very close to zero implies capacitors so big that it's not possible the design en VLSI.

## 2 Algorithm LMS

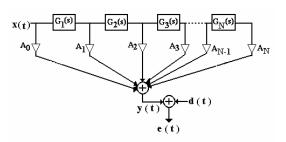

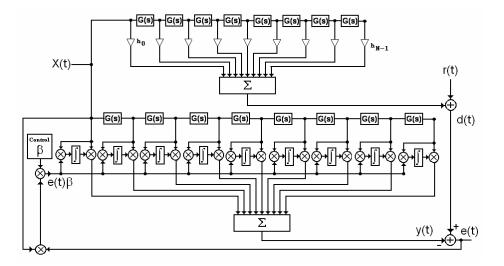

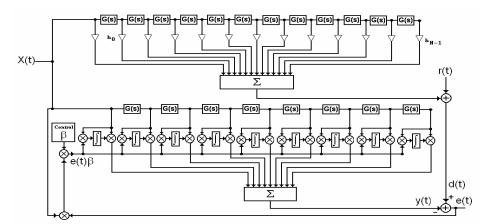

Consider the output signal of the generalized transverse filter shown in figure 1, whose Laplace transform is given by:

$$Y(s) = \sum_{k=0}^{N-1} A_k G_k(s) X(s)$$

(2.1)

Where  $G_k(s)$  is the transference function of the k-th phase, X(t) is the Laplace transform of the input signal and  $A_k$  are the weights of the k-th stage.

Fig. 1 Generalized transverse filter

#### 2.1 Adaptation Algorithm

Among the most common algorithms used; we have those based in the search of the gradient of which the LMS algorithm is its major exponent. It is due mainly to its robustness and low computing complexity [3]. The expression to calculate the  $A_k$ with the LMS continuous time is given by [4].

$$A_k(t) = \beta \int_0^t e(\tau) x_k(\tau) d\tau$$

(2.1)

Where  $e(\tau)$  is the output error of the system and  $x_k(\tau)$  is the output signal of the k-th phase of the filter shown in figure 1 and  $\beta$  is a factor that controls the stability and adaptation velocity of the algorithm and may be written as:

$$\beta = \frac{\alpha}{X^{T}(t)X(t)}$$

(2.2)

Where  $\alpha$  is the convergence factor of the algorithm and X(t) is the input vector, in this way the algorithm given by the equation (2.1) converges to its optimum value of  $0 < \alpha < 2$  [5]. The convergence conditions [6] may be written as:

$$v_k(t) = w_k^* \left[ 1 - \exp(-\beta \lambda_k t) \right] k = 1, 2, ..., N$$

(2.3)

Where  $\lambda_k$  the k-th is own value of the matrix of selfcorrelation of the input signal and  $w_k^*$  is the optimum value of the k-th component of the vector coefficients. The LMS algorithm of continuous time converges if  $\beta > 0$ . The condition of convergence derived from the equation (2.3) guarantee that the average value of the vector of the coefficients that converge to the solution of the Wiener-Hopf equation, but do not show the quantity of distortion that will remain in the weights due to the noise produced in the estimate of the instant gradient after the convergence has been obtained. An approximate value, valid for the small values of  $\beta$  is given by [6], [7].

$$E\left[V(t)V^{T}(t)\right] = \beta\xi_{\min}I \qquad (2.4)$$

Where  $\xi_{\min}$  is the value of the minimum half quadratic error which, when the order of the filter is chosen properly is very closed to the power or capacity of the additive noise and I is the identity matrix and V(t) is the error vector [7]. The noise of the weights will cause in addition an error in the output of the system that is given by [8]:

$$\xi_{excess} = \beta \xi_{\min} \left( E \Big[ X(t) X^{T}(T) \Big] \right)$$

(2.5)

Substituting the equation (2.1) in (2.5) we have:

$$\xi_{excess} = \frac{\xi_{\min} \alpha \left( X^T(t) X(t) \right)}{T^T(t) X(t)} = \alpha \xi_{\min}$$

(2.6)

In that way the power of the additional error in the output of the system due to the noise of the weights of the system, will be proportional to the product of the powers or capacities of additive noise and of the convergence factor  $\alpha$ .

#### **3 Modular structures**

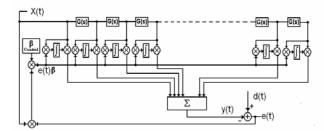

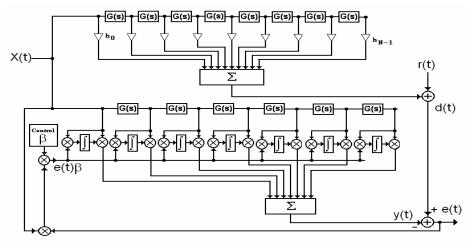

The structure shown in figure 2 represents the proposal of an adaptable analog modular filter, where each of its basic elements is connected among them. The basic modules of the analog filter are established by: **a**) the delay line, **b**) the analog adaptation LMS algorithm, **c**) multipliers, integrators and analog adders, **d**) the module of velocity control of convergence [8].

Fig. 2 Adaptive analog modular filter

#### 3.1 Analog delay

For the modules that represent each analog delay, they are designed in such ways that are made with a

VLSI circuit. The input signal should be delayed enough so that the LMS algorithm converges.

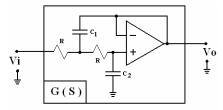

The analog delay is based in the design of a low-pass filter of a second order with a low frequency pole of 100 KHz in order to process low frequency voice or audio signals (cutoff frequency) type Butterworth [9] as shown in figure 3.

Fig. 3 Structure of an analog delay

The function transference H(s) of the low-pass filter may be written as [10]:

$$H(s) = \frac{k\omega_0^2}{s^2 + \left(\frac{\omega_0}{Q}\right)s + \omega_0^2}$$

(3.1)

For the calculation of the capacitors shown in figure 3, its proposed a resistor (R) the 10 K $\Omega$ , then 1 the capacitor value that are given in function of the Butterworth polynomials are:  $C_1 = 225 \, pF$ ,  $C_2 = 112 \, pf$  substituting the capacitors and resistors in equation (3.1) and this may be written as:

$$H(s) = \frac{V_{out}}{V_{in}} = \frac{1}{1 - \omega^2 \left(R^2 C_1 C_2\right) + s C_2(2R)}$$

(3.2)

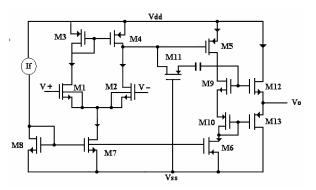

The operational amplifier used in the low-pass filters was designed in a way that it would fulfill or carry out the integration requirements in VLSI. In figure 4 we see the internal structure of the operational amplifier [11]; a CMOS technology of HP of 0.5  $\mu$ m was used, the electric characteristics of the structure in figure 4 are shown on table 1.

For the operational amplifier design, the relationship width-length (W/L) of transistors was calculated [11]. The value of L of 4  $\mu$ m was considered for all the transistors, the calculation of its width of figure 4 is shown on table 2

Fig. 4 Internal structure of operational amplifier.

Table 1 Characteristics of the operational amplifier

| Parameters                      | Values   |

|---------------------------------|----------|

| Unit Gain Frequency             | 7.41 MHz |

| Low frequency pole              | 21.88 Hz |

| Open loop gain (G)              | 112.5 dB |

| Dynamic range differential pair | ± 100 mV |

| Output impedance                | 111 Ω    |

| Slew rate (Sr)                  | 2.2 v/µs |

| Power dissipation               | 7.917 mW |

| Closed loop gain (-3dB)         | 7.17 MHz |

Table 2 Dimensions of width (W)

| $M_1 = M_2 = 225 \mu m$ | $M_3 = M_4 = 101 \mu m$ |

|-------------------------|-------------------------|

| $M_5 = 585 \mu m$       | $M_6 = 20.7\mu m$       |

| $M_7 = M_8 = 6.3 \mu m$ | $M_9 = 30 \mu m$        |

| $M_{10} = 37 \mu m$     | $M_{11} = 18.3 \mu m$   |

| $M_{12} = 300 \mu m$    | $M_{13} = 370 \mu m$    |

| $C_c = 5 pF$            |                         |

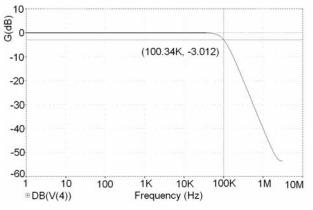

Figure 5 shows the response in the frequency domain analog delay circuit, we may observe that the cutoff frequency in the simulation realized in PSpice is of 100.34 KHz.

Fig. 5 Response of analog delay circuit in frequency

Figure 6 shows the complete delay line, the delay between the input and output signal is of  $3.35\mu$ s for each block.

Fig. 6 Analog delay line with eight delays

#### **3.2 Analog Integrator**

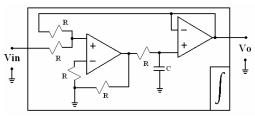

The proposal of the integrator is shown in figure 7 it is formed by two operational amplifiers [12], one of them is used in the addition circuit and another as impedance coupler, a first order low-pass net is used.

Fig. 7 Structure of analog integrator

The transference function of figure 7 is:

$$\frac{V_o(s)}{V_i(s)} = \frac{k \frac{A(s)}{A(s)+1}}{s+k-k \frac{A(s)}{A(s)+1}}$$

(3.3)

Where A(s) is the open loop gain of the operational amplifier and may be expressed as:

$$A(s) = \frac{GB}{s} \tag{3.4}$$

GB is the gain product band width, substituting the equation (3.4) in (3.3) we obtain:

$$\frac{V_{o}(s)}{V_{i}(s)} = \frac{\omega_{p}}{s^{3} \frac{1}{(GB)^{2}} + s^{2} \left(\frac{2}{GB} + \frac{\omega_{p}}{(GB)^{2}} + \left(1 + \frac{2\omega_{p}}{GB}\right)\right)}$$

(3.5)

From here  $\omega_p$  is the cut frequency of the low-pass filter and may be written as:

$$\omega_p = \frac{1}{RC} \tag{3.6}$$

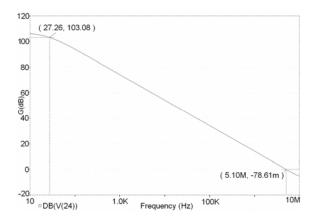

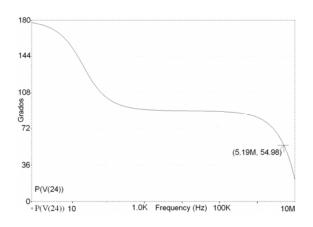

As we are looking for the possibility to integrate this circuit in VLSI, then the capacitor value (C) must be of a few picofarads; for example of 5pF and the resistor (R) could be of a 1K $\Omega$  value [7], the operational amplifier used is the same as in figure 5. The response of the integrator in magnitude and phase may be seen in figures 8 and 9, the structure is independent from the position of the low frequency pole, the transference function and it only affects the output signal amplitude it can be observed that the circuit really acts as an integrator from 27 Hz to 5.1 MHz and that the phase is approximately 55°.

Fig. 8 Response in frequency of the analog integrator

Fig. 9 Phase of the analog integrator

# **3.3** Analog multiplier of four quadrants in voltage mode.

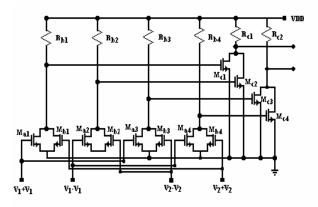

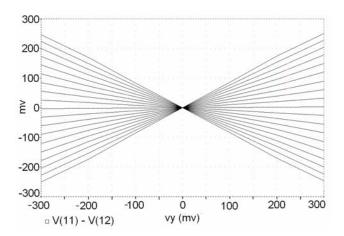

The analog multipliers have great variety of applications; they are programming elements in systems with analog adaptive filters, digital filters and neural networks. For the application of the identifier a four quadrants multiplier in voltage mode was used. Figure 10 shows the multiplier structure; figure 11 presents the dc behavior response of the multiplier [13]. In Table 3, the width dimensions (W) of the transistors are shown, table 4 shows the length (L) of the transistors of the analog multiplier.

Table 3 Width dimensions (W) of the transistors and resistors values

| $M_{a1,2,3,4}M_{b1,2,3,4} = 60\mu m$ | $M_{C1,2,3,4} = 19 \mu m$ |

|--------------------------------------|---------------------------|

| $R_{b1,2,3,4} = 2.8K\Omega$          | $R_{C1,2} = 6.1K\Omega$   |

Table 4 Length (L) dimensions of the transistors

| $M_{a1,2,3,4}M_{b1,2,3,4} = 6\mu m \qquad \qquad M_{C1,2,3,4} = 2\mu m$ |

|-------------------------------------------------------------------------|

|-------------------------------------------------------------------------|

Fig. 10 Structure of four quadrants multiplier

Fig. 11 Multiplier response in dc

The voltage at the output of figure 10 may be written [11], [13] as:

$$V_{out} = \begin{cases} 1 - \frac{3}{2} (V_1 - V_T) \theta_a - \frac{3}{2} (V_2 - V_T) \theta_b \\ - \begin{bmatrix} R_b K_a (V_1 - V_T)^2 + R_b K_b (V_2 - V_T)^2 \\ -V_{DD} + V_T \end{bmatrix} \theta_c \end{cases} k' v_1 v_2 \\ - \begin{bmatrix} \frac{1}{2(V_1 - V_2)} \theta_a + 3R_a K_a \theta_c \\ - \begin{bmatrix} \frac{1}{2(V_2 - V_T)} \theta_b + 3R_b K_b \theta_c \end{bmatrix} k' v_1 v_2 \end{cases}$$

(3.7)

Where  $\theta_a$ ,  $\theta_b$  and  $\theta_c$  is mobility reduction of transistors, k' multiplication constant,  $V_t$  the threshold voltage,  $v_1$  and  $v_2$  the input signals to the multiplier.

## **3.4 Modeling and simulation of the analog adaptive filter configured as identifier.**

Here is presented the module design of an analog adaptive filter configured as an identifier, for this configuration three cases are presented: 1) is a low-pass filter with eight analog delays and eight coefficients for the update of the algorithm weights LMS as shown in figure 12, 2) a low-pass filter with eight analog delays and six coefficients for bringing up to date the weights of the algorithm LMS and 3) a low-pass filter with twelve analog delays and eight coefficients that bring up to date the weights of the LMS algorithm. These three cases were simulated under the following Pspice parameters; an FM input signal (0,100m, 200M, 3, 10K) with a modulation index of 3 and a gain of 0.5 for the weights of the low- pass filter and  $\beta$

Fig. 12 Adaptive filter used as identifier

Fig. 13 Adaptive filter with twelve delays in the filter and eight coefficients in the LMS algorithm

Fig. 14 Adaptive filter with twelve delays in the filter and eight coefficients in the LMS algorithm.

#### **3.5 Results**

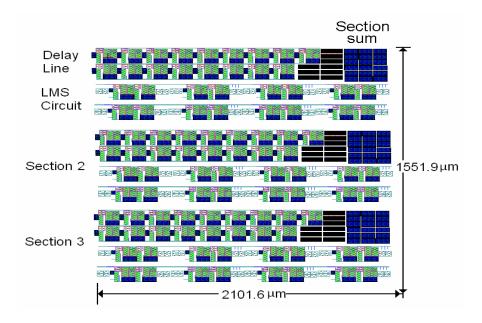

The next results are the evaluation of analog adaptive filter configured as an identifier from layout designed. Recently was presented PSpice simulations results only [14]

In figure 15, the layout circuit is shown with three sections of analog LMS adaptive filter; each one includes: one delay line with eight taps, the analog adder, and analog LMS circuit. In references [15]-[17] other circuits can be seen for this type of applications.

Fig 15 Layout of the adaptive filter

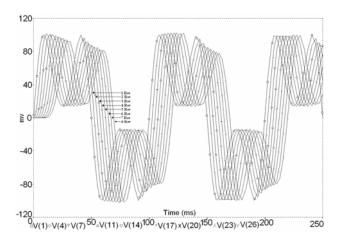

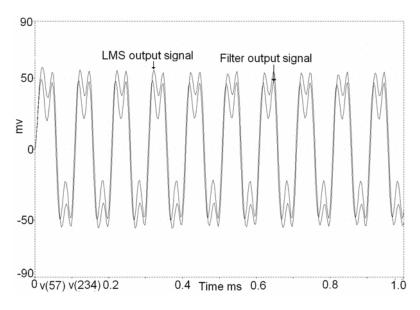

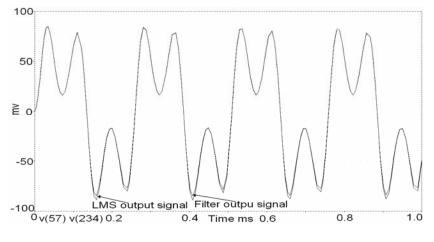

Figure 16 shows the response in time of the structure of figure 12. We may appreciate how the estimated signal has a very good approximation to

the reference signal; this is reached starting from the  $40\mu$ s that is when we obtain the convergence of the algorithm[15].

Fig. 16 Identifier output, first case

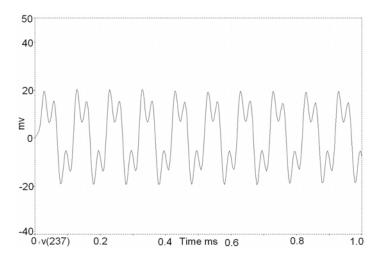

Figure 17 shows the algorithm error derived from the simulation that is approximately  $\pm 2.4$  mV, the

energy consumption is of 0.622 watts [16].

Fig.17 Output error of system, layout first case

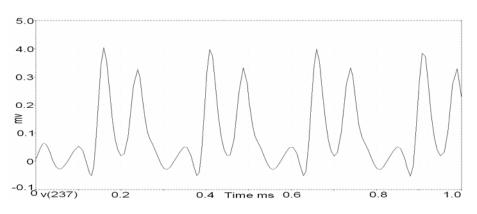

For the second case in figure 18 is shown the response in time domain of the structure of figure 13, we may appreciate how the estimated signal has an approximation to the reference signal, this is reached beginning from  $50\mu$ s that is when we can

obtain the convergence of the algorithm. In figure 19 we observe the algorithm error derived of the simulation that is approximately  $\pm$  20mV, the energy consumption is of 0.520 watts [17].

Fig. 18 Identifier output, second case

Fig. 19 Output error of system, layout second case

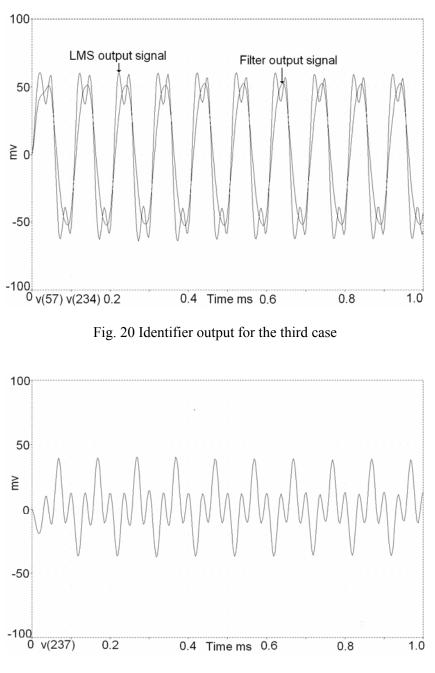

For the third case figure 20 shows the response in the time domain of the structure of figure 14, we may appreciate how the estimated signal does not have an approximation to the reference signal this is reached starting from the  $60\mu$ s that is, when the convergence of the algorithm is obtained. In figure 21 we may see the algorithm error derived from the simulation that is approximately of  $\pm$  37mV the energy consumption of the circuit is of 0.680 watts.

Fig. 21 Output error of system, third case

### 4. Conclusions

The analog LMS adaptive filter designed shows a very good convergence speed in predictor configuration. The size of overall circuit and the low power consumption shows that is possible use this circuit in portable equipment for mobile communications. Is reasonable think that the circuit can be used in analog echo chancellors or equalizers to improve the quality in mobile communications systems or wireless broadband networks.

## References

- [1] Carusone and Johns D. A, "Analogue Adaptive Filters: Past and Present", IEEE Proc. Devices Syst., Vol. 147, No. 1, pp. 82-90, February 2000.

- [2] Jeronimo Arenas-Garcia, Vanessa Gomez-Verdejo, and Aníbal R. Figueiras-Vidal, "New Algorithms for Improved Adaptive Convex Combination of LMS Transversal Filter", IEEE Transactions on Instrumentation and measurement, Vol. 54. No 6, pp 2239-2249, December 2005.

- [3] Bernard Widrow and Max Kamenetsky, "On the Statical Efficiency of the LMS Family of Adaptive Algorithms", 0-7803-7898-9/03/2003, pp2872-2880.

- [4] Mahesh Godavarti, and Alfred O. Hero, "Partial Update LMS Algorithms", IEEE Transactions on signal processing, Vol. 53, No. 7, pp 2382-2399, July 2005.

- [5] Nino Luis , Perez Hector and Edgar Sanchez-Sinencio, "Continuous Time Normalized LMS adaptive Filter Structure", Journal of Signal Processing, Vol. 2, No.4, pp. 309-317, July 1998.

- [6] Nino Luis, Perez Hector and Sanchez Edgar, "A Modular Analog NLMS Structure for Adaptive Filtering", Journal of Analog Integrated Circuits and Signal Processing, Kluwer Academic Publishers, Vol. 21, pp.127-142. 1999.

- [7] Perez Efren, Sanchez Juan, Nino Luis and Hector Perez, "A Continuous Time VLSI Integrator for Adaptive Signal Processing", Proceedings of international Symposium on Information Theory and its application, Vol. 1, pp 301 – 304, 1998.

- [8] Sanchez Juan C., Hector Perez, Luis Nino and Alejandro Diaz, "A new VLSI Integrator Circuit for analog signal processing", Conilecom 2000/Universidad de las Américas, Puebla 2000.

- [9] S. C. Martin S. Jr. R. Gordon L. Carpenter, Electronic Design and System, second edition, Addison-Wesley Iberoamerica 2002.

- [10] Horenstein Nark N., Oscillator and filter, Microelectronic device and circuit, Prentice – Hall Hispanoamerica, S.A, USA 1997.

- 11] Gregorian Roubik, Temes Gabor C., MOS operational amplifiers, Analog MOS integrated circuits for signal processing, A Wiley–Interscience publication, 1986.

- [12] Perez Jose, Sanchez Juan, Mercado Ernesto, Lopez Osvaldo, Beltran Lourdes, "The circuit integrator analog VLSI comparison the structure", The Mexican Journal of Electromechanical Engineering Vol 6. No 4, pp. 169-174, 2002 ESIME-IPN.

- [13] Lopez Osvaldo, Perez Jose, Vazquez R., "Multiplier analog the analysis for processing applications the signal VLSI" The Mexican Journal of Electromechanical Engineering, Vol. 9, No. 3, pp. 125-133, 2005 ESIME-IPN.

- [14] Jose Perez-Carmona, Hector Perez-Meana, Juan Sanchez Garcia, "Modular design of an adaptive analog filter shaped as an identifier with CMOS of 0.5μm", New Aspects of circuits, Proceedings of 12th WSEAS International Conference on Circuits, pp. 224-231, July 2008.

- [15] F. Mohd-Yasing, M.T. Yap, M.B.I. Reaz, "CMOS Instrumentation Amplifier with Offset Cancellation Circuitry for Biomedical Application", WSEAS Transactions on Circuits and Systems, Issue 1, Volume 6, pp. 171-179, January 2007.

- [16] Kwisung Yoo, Dongmyung Lee, Gunhee Han, Sungmin Park, "Design of a 10Gbps Analog Adaptive Equalizer and a Pre-Emphasis Filter for 34-inch Backplane Channel",WSEAS Transactions on Circuits and Systems, Issue 12, Volume 5, pp.1719-1725, December 2006.

- [17] Franz Schlogl, Horst Dietrich, Horst Zimmermann, "Two-Signal-Path Three-Stage OpAmp in 120nm Digital CMOS with Two-Stage Gain-Boost",WSEAS Transactions on Circuits and Systems, Issue 10, Volume 5, pp. 1563-1569, October 2006.