# **On Bifunctional Polymorphic Gates Controlled by a Special Signal**

RICHARD RUZICKA Faculty of Information Technology Brno University of Technology Bozetechova 1, CZ-61266, Brno CZECH REPUBLIC ruzicka@fit.vutbr.cz http://www.fit.vutbr.cz/~ruzicka

*Abstract:* - Polymorphic digital circuits are circuits composed of polymorphic (multifunctional) as well as ordinary gates. In addition to its standard logic function (such as NAND), a polymorphic gate exhibits another logic function which is activated under a specific condition, for example, when Vdd, temperature, illumination or a special signal reaches a certain level. This paper describes existing polymorphic gates and their features, benefits and limits and discusses special class of polymorphic gates – bifunctional polymorphic gates controlled by a special signal. These gates seem to be most flexible polymorphic gates. In the paper a new two-input bifunctional gate for polymorphic circuits is proposed. The gate produces NAND or XOR function according to a special signal. The proposed gate is effective in terms of area overhead – it consists of 9 transistors only, while corresponding circuit employing conventional gates consists of more than 10 transistors.

Key-Words: hardware engineering, digital circuits, CMOS logic gates, polymorphic electronics, VLSI, reconfigurable digital circuits

## **1** Introduction

Polymorphic digital circuits are circuits composed of polymorphic (multifunctional) gates. In addition to its standard function (e.g. NAND), a polymorphic gate exhibits another logic function (e.g. NOR) which is activated under a specific condition, for example, when Vdd, temperature or a special signal reaches a certain level. The concept of polymorphic gates was proposed by Stoica et al [1]. Polymorphic gates are able to perform one or more additional functions in addition to the "main" function of the circuit. A function change does not require switches/reconfiguration as in traditional approaches. Instead, the change comes from modifications in the characteristics of devices involved in the circuit (mainly transistor operation point), in response to controls such as temperature, power supply voltage (Vdd), control signals, light, etc. The structure of the circuit remains the same. For example, NAND/NOR gate was proposed which operates as NAND when Vdd = 3.3V and as NOR when Vdd = 1.8V. It consists of 6 transistors connected in an unconventional structure [2]. In theory, it could be possible to build a polymorphic gate that implements k different logic functions in k different environments. Practically, k is 2 or 3 nowadays (bi- or trifunctional gates).

Research papers indicate many areas in which polymorphic gates could be utilized. The following list provides some examples (see a thorough analysis in [1, 3]): • The automatic control of power consumption when battery voltage decreases (a circuit realizes another function for lower battery voltage; however, its structure remains unchanged).

• Implementation of a hidden function, invisible to the user, which can be activated in a specific environment (e.g. watermarking at the hardware level).

• Intelligent sensors for biometrics, robotics, industrial measurement, etc.

• Reverse engineering protection.

• Implementation of low-cost adaptive systems that are able to adjust the behavior inherently.

When bifunctional polymorphic gates controlled by a special signal are employed, some other areas of digital polymorphic electronics arise:

• Smart reconfiguration without multiplexers or switches.

• On-line diagnostics for fault-tolerant and safe systems, self-checking circuits [11, 12].

There are two main problems in polymorphic circuit design:

1. design of generally usable polymorphic gates as building blocks of digital polymorphic circuits and

2. suitable and efficient design techniques for design of digital polymorphic circuits.

Considering polymorphic gates as building blocks offers an opportunity to design digital polymorphic circuit at gate level. Almost all existing circuits [6,7,8] were designed by some unconventional design techniques such as evolvable hardware [5] etc – see

section 2. So solution of the 2nd problem is still under research. This paper proposes contribution to the solution of the 1st problem. Note that no circuits more complex than a single gate have been reported that are designed at the transistor level.

The paper is organized as follows: Section 2 introduces state-of-the-art of polymorphic electronics; section 3 presents known and published polymorphic gates, its advantages and disadvantages. Section 4 introduces a special class of polymorphic gates – bifunctional polymorphic gates controlled by a special signal. Section 5 describes newly proposed polymorphic NAND/XOR gate. In section 6, simulation results of the proposed gate are presented. Section 7 shows some example of the gate utilization and section 8 concludes the paper.

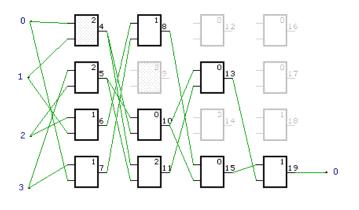

Figure 1: Example of evolved polymorphic circuit with three polymorphic gates (marked "0").

#### **2** Polymorphic circuits

Polymorphic circuits are multifunctional circuits. The change of their behavior comes from modifications in the characteristic of components (e.g. in a transistor's operation point) involved in the circuit in response to controls such as temperature, power supply voltage, light, a special signal etc. [1, 3]. No conventional approach has been proposed to the design of polymorphic gate-level circuits so far. However, simple polymorphic modules have been designed by means of evolutionary design techniques [10]. To produce some useful results, cartesian genetic programming (CGP) has been utilized. In CGP, the circuit is modeled as an array of u (columns)  $\times v$  (rows) of programmable elements (gates). The number of circuit inputs,  $n_i$ , and outputs,  $n_o$ , is fixed. Feedback is not allowed. Each gate input can be connected to the output of some gate placed in the previous columns or to some of circuit inputs. Each gate is programmed to perform one of functions defined at the beginning of the experiment. Every individual is encoded using  $u \times v \times 3 + n_o$  integers. Only a mutation

operator is applied which changes one gene of the chromosome. In case of combinational circuit evolution, the fitness function is constructed to minimize the Hamming distance between output vectors of a candidate circuit and the required output vectors. Typically, all possible input vectors are applied to obtain the set of output vectors for the both required functions  $f_1$  (in mode 1) and  $f_2$  (in mode 2).

Fig. 1 shows an example of evolved circuit. The circuit utilizes ten gates; three of them are polymorphic (marked "0"). When Vdd = 1.2V, the polymorphic gates operate as NANDs and the circuit implements the parity function. When Vdd = 3.3V, the polymorphic gates operate as NORs and the circuit implements the majority function. In both modes, circuit topology as well as functionality of other gates remains unchanged. Therefore, the circuit integrates a sensing ability with a logic function [7].

#### **3** Known Polymorphic Gates

In the recent years, several polymorphic gates have been discovered. Table I shows existing polymorphic gates. Practically all of them are proposed by authors of polymorphic electronics approach – Adrian Stoica, Ricardo Zebulum and Didier Keymeulen from NASA JPL. These gates are designed by evolutionary approach, some of them in FPTA.

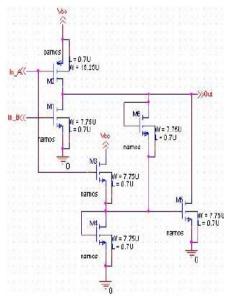

Lot of these gates has very unconventional structure for example, see Fig. 3. The NAND/NOR gate shown in this figure is probably the most famous example of a polymorphic gate. This gate and also practically all gates shown in the Table 1 permits low transistor count (note that the common NAND and NOR gates cost 4 transistors, the XOR gate can be implemented using 6-10 transistors and 2 transistors are needed to create the inverter in the standard CMOS technology) but their structure brings some problems such as weak output logic levels, higher power consumption and lower input impedance. Some of gates from Table 1 were simulated and results were not very satisfactory. Furthermore, lots of them are also strongly dependent on used technology (predominantly HP 0.35 micron) and parameters of transistors (especially channel width and length). It can be one of reasons why simulations were not too successful.

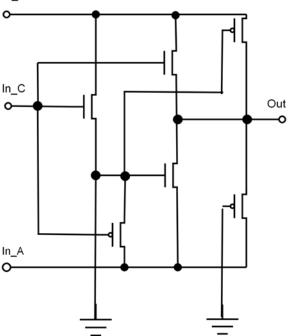

Note that for example AND/OR gate controlled by an ext. signal (see Fig. 2) behaves as three-input logic gate, where the third input (In\_C) serves as input of the signal that controls the function. When this input is at high, the gate produces AND function, when the input C is at low, the gate produces OR function of two remaining inputs. It can be seen that the structure in Fig. 2 indicates some potential problems (e.g. output logic levels are inherited from input levels, not from Vdd/Gnd as usual).

| Gate             | Conditions of Function Change    | No. of Transistors | Published In |

|------------------|----------------------------------|--------------------|--------------|

| AND/OR           | 27/125°C Temperature             | 6                  | [3]          |

| AND/OR/XOR       | 3.3/0.0/1.5V External signal     | 10                 | [3]          |

| AND/OR           | 3.3/0.0V External signal         | 6                  | [1]          |

| NAND/NOR/XOR/AND | 0.0/0.9/1.1/1.8V External signal | 11                 | [4]          |

| AND/OR           | 1.2/3.3V – Vdd                   | 8                  | [3]          |

| NAND/NOR         | 3.3/1.8V – Vdd                   | 6 (fabricated)     | [2]          |

Table 1 - Published Polymorphic Gates

## 4 Bifunctional Polymorphic Gates Controlled by a Special Signal

The function of the bifunctional polymorphic gate controlled by a special signal depends on the level at a special logic input similarly to AND/OR gate mentioned in the previous chapter (Fig. 2). It makes the gate more flexible in terms of conditions under which the function is changed. If the function may be depending on Vdd ore temperature, certain level may be detected by a detector and the detector then may control the function-switching input of the gate. Of course, only one detector can be employed for the whole circuit. If the proposed gate functions switching may be used for some kind of reconfiguration (circuit function change on demand), it may be simply reached by controlling of functionswitching inputs of all employed polymorphic gates.

Bifunctional polymorphic gates controlled by a special logic signal should be also employed in digital circuits which have one function only. One alternative is to use bifunctional polymorphic gate as ordinary gate with three logic inputs which exhibits an unconventional logic function. The main benefit is implementation cost - bifunctional polymorphic gate is cheaper than a net of conventional gate with the same function. Another alternative are self-checking circuits employing polymorphic gates. The goal is to obtain a circuit which exhibits the same function in both polymorphic gates' modes of operation. Moreover, when the circuit is faulty, changing of polymorphic gates' mode of operation causes value changing on some output. To check such a circuit is then very simple – just change the polymorphic gates' mode switching signal and detect output changing [12]. These opportunities make bifunctional polymorphic gates controlled by a special signal most flexible polymorphic gates.

## 5 Newly Proposed NAND/XOR Polymorphic Gate

A new polymorphic gate was proposed for our purposes. The gate has two optional functions – NAND and XOR. Both these functions are widely applicable, besides it, NAND is logic-complete. It predetermines the gate for wide usage in many applications. The gate is bifunctional polymorphic gate controlled by a special signal.

The gate consists of 9 P-MOS and N-MOS transistors. It is CMOS-compatible. Output of the gate is designed as true complementary pair. It guarantees good quality of output signal under usual conditions. The structure of the gate is shown in Fig. 4. The mode switching signal should be connected to input "In\_C", then inputs "In\_A" and "In\_B" are logic variables inputs (see Fig. 3). When the input "In\_C" is at low, the gate produces "In\_A" NAND "In\_B" at the output "Out", when the input "In\_C" is at high, the gate produces "In\_A" XOR "In\_B" at the output "Out".

Figure 2: AND/OR gate controlled by a special signal proposed in [1].

Figure 3: Structure of NAND/NOR gate proposed in [2]

Figure 4: Structure of a newly proposed NAND/XOR gate

#### 6 Gate Simulation and Experiments

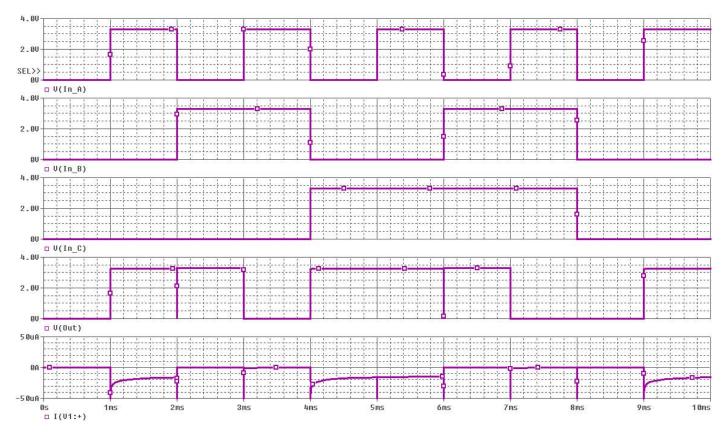

The proposed gate (see Fig. 4) was simulated using OrCAD PSpice 10.3 from Cadence and BSIM2 MOS transistor model from AMIS07 library. In Fig. 4 simulated waveforms for the proposed gate can be seen. Simulations show that the proposed gate meets requirements set in the first assignment. The gate operates reliably for Vdd > 2.5V and up to hundreds of MHz. The gate is not too temperature dependent, of course, higher temperature causes lower operation frequency. Generally, the gate overcomes previously published gates in many parameters and it appears to be really applicable in real circuits. One minor disadvantage could be slightly higher power consumption in some states. This is also feature inherited from 6-transistors XOR gate. When the transistor M6 (see Fig. 4) is used to

transfer low logic level, then transistor M9 is not fully opened and M8 is not fully closed. Then the gate consumes  $15 - 20 \ \mu$ A (see Fig. 5). In my opinion this is acceptable and it is very good result in comparison with previously proposed polymorphic gates. Fig. 5 shows simulated waveforms for the proposed gate.

### 7 Example of the Newly Proposed NAND/XOR Gate Utilisation

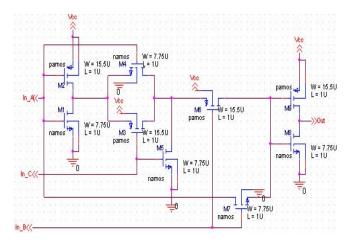

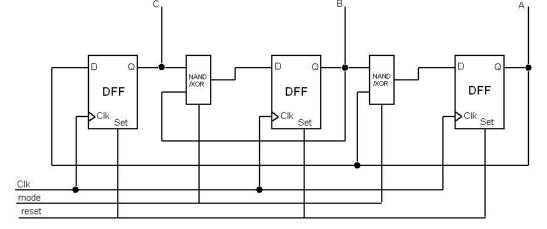

Here is a little example of utilization of the proposed polymorphic NAND/XOR gate. It is sequential digital circuit, which can be used as a controller. The circuit in Fig. 6 is a kind of three-bit counter. It changes its state (state of three D-type flip-flops) each clock pulse. Glue logic, 2 two-input gates, reduces the number of states.

Let us imagine that a seven-state controller is needed for an application, but under special conditions (e.g. when battery is low or circuit temperature is high), it is needed to skip two less important states. So under special conditions, only five-state counter is needed. In the conventional design approach, multiplexing of two separated counters/controllers or at least two glue/logic blocks of one counter to reconfigure the controller is needed. But polymorphic electronics offers more cheaper and smarter solution of the problem. Fig. 6 shows ordinary three/bit counter at the first sight. If two gates in the circuit shown in Fig. 6 are XORs, the counter has seven states. If these gates are NANDs, the counter has five states. If proposed polymorphic NAND/XOR gates are employed, the counter should be easily switched between two modes - seven- or fivestate counter. Note that no structure reconfiguration or change is needed. Circuit function switching is done by changing of gate function only. Structure remains unchanged. This is typical attribute of polymorphic circuits.

Of course, above-described seven/five-state counter could be implemented using standard logic. But solution employing proposed polymorphic NAND/XOR gates is cheaper than any conventional solution in terms of transistor count/chip area. While one proposed polymorphic NAND/XOR gate consists of 9 transistors, ordinary NAND gate consists of 4 and ordinary XOR consist typically of 6 transistors [9]. Moreover several transistors are needed to switch between these two gates/functions (2-input multiplexer is typically implemented using 6 transistors). In comparison with solution employing two switched complete controllers more than 50% of chip area is saved. In comparison with solution employing switched glue logic with ordinary NAND and XOR gates, more than 20% of chip area is saved.

Figure 5: Simulation waveform for the proposed NAND/XOR polymorphic gate (Vdd = 3.3V, f = 1kHz, T =  $20^{\circ}C$ )

Figure 6: An example of polymorphic counter/controller employing proposed polymorphic NAND/XOR gate

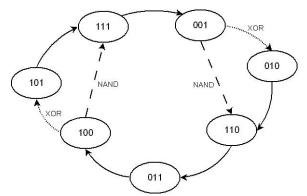

In Fig. 7, transition diagram is shown. Each transition is executed by a clock pulse. There are two states in the figure, for which the next state depends on the mode of polymorphic gates – state "001" and "100". Dashed transitions show what happens when polymorphic gates are in "NAND" mode. In this mode, states "010" and "101" are skipped and the counter passes directly to states "110" and "111" respectively. Dotted transitions show full cycle of the counter (all seven states) when polymorphic gates are in "XOR" mode. When the counter is in one of "extended" states ("010" or "101"), next clock pulse causes transition to "110" or "111" regardless of the mode of polymorphic gates.

Figure 7: Transition diagram of the counter from Fig. 4

## 8 Conclusion

Polymorphic electronics is a new field of electronics. Especially in digital circuits field, it brings a new possibilities to design efficient circuits with various features such as smart reconfiguration, self-checking modules, watermarking, intelligent sensors etc. In the paper, a new bifunctional polymorphic gate controlled by a special signal was proposed. The gate has three inputs. It can be used as polymorphic bifunctional twoinput gate, which performs NAND or XOR function according to the mode expressed by the state of the third input or as three-input logic gate which exhibits a special logic function. In contrary to previously introduced polymorphic gates, the gate is robust; it inherits features from ordinary CMOS 6-transistors XOR gate [9]. The proposed gate has CMOS compatible output. The main contribution of this newly proposed gate lies in implementation cost. As a replacement of both NAND and XOR gates with switch, it consists of 9 transistors only. Ordinary NAND gate consists of 4 and ordinary XOR gate consists of 6 transistors. It is 10 transistors without the switch. The gate was simulated using Cadence OrCAD PSpice 10.3 and BSIM2 transistor model from AMIS07 library (0.7 micron technology). A small example shows how the utilisation of the proposed gate in a small and simple but frequently used circuit can save a significant number of transistors in compare with the conventional solution. For future work, fabrication of proposed gate is intended using CMOS 0.7 micron technology.

### Acknowledgements

This work has been supported by the Grant Agency of the Czech Republic under No.102/06/0599 "Methods of polymorphic digital circuit design" and by Research Plan No. MSM 0021630528 "Security-Oriented Research in Information Technology".

#### References

- [1] Stoica, A., Zebulum, R. S., Keymeulen, D., Polymorphic electronics. Proc. of Evolvable Systems: From Biology to Hardware Conference, volume 2210 of LNCS, Springer 2001, pp. 291–302.

- [2] Stoica, A., Zebulum, R. S., Guo, X., Keymeulen, D., Ferguson, I., Duong, V., Taking evolutionary circuit design from experimentation to implementation: Some useful techniques and a silicon demonstration.

IEE Proc.-Comp. Digit. Tech., 151(4), 2004, pp. :295-300.

- [3] Stoica, A., Zebulum, R., Keymeulen, D., Lohn, J., On polymorphic circuits and their design using evolutionary algorithms. Proc. of IASTED International Conference on Applied Informatics (AI2002). Insbruck, Austria, 2002.

- [4] Stoica, A., Zebulum, R., Four-function logic gate controlled by analog voltage. NASA New Technology Report NPO-40772, NASA's Jet Propulsion Laboratory, Pasadena, California. http://www.afrlhorizons.com/ETB/ETBriefs/Mar06/ NPO\_40772.html

- [5] Sekanina, L., Martinek, T., Gajda, Z., Extrinsic and intrinsic evolution of multifunctional combinational modules. 2006 IEEE World Congress on Computational Intelligence, IEEE CIS, 2006, pp. 9676-9683.

- [6] Sekanina, L, Starecek, L., Kotasek, Z., Novel logic circuits controlled by Vdd. 2006 IEEE Design and Diagnostics of Electronic Circuits and Systems Workshop, Prague, CZ, IEEE CS, 2006, pp. 85-86.

- [7] Sekanina, L., Starecek, L., Gajda, Z., Kotasek, Z., Evolution of multifunctional combinational modules controlled by the power supply voltage. 1st NASA/ESA Conference on Adaptive Hardware and Systems, Piscataway, US, IEEE CS, 2006, pp. 186-193.

- [8] Ruzicka, R., Sekanina, L., Evolutionary circuit design in REPOMO - Reconfigurable Polymorphic Module. The Second IASTED International Conference on Computational Intelligence, Anaheim, US, ACTA Press, 2006, pp. 237-241.

- [9] Neil H.E., Weste and Kamran Eshraghian, Principles of CMOS VLSI design. Addison-Wesley, 1992.

- [10] L. Sekanina. Design Methods for Polymorphic Digital Circuits. In Proc. of the 8th IEEE Design and Diagnostics of Electronic Circuits and Systems Workshop DDECS 2005, pp. 145–150, Sopron, Hungary, 2005. University of West Hungary.

- [11] Sekanina Lukáš: Design and Analysis of a New Self-Testing Adder Which Utilizes Polymorphic Gates, In: 2007 IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems, Gliwice, PL, IEEE CS, 2007, pp. 243-246

- [12] Sekanina Lukáš: Evolution of Polymorphic Self-Checking Circuits, In: Lecture Notes in Computer Science, 2007, No. 4684, DE, pp. 186-197