# Improved Characteristics of Ultra-Thin Cerium Dioxide with Rapid Thermal Annealing

Kuo Cheng Chiang, Jer Chyi Wang, and Tan Fu Lei

Department of Electronic Engineering and Institute of Electronics National Chiao Tung University, Hsinchu, Taiwan, R.O.C.

## ABSTRACT

In this study, the characteristics of ultra-thin cerium dioxide with rapid thermal annealing are investigated. The cerium dioxide film with post-deposition rapid thermal annealing exhibits the thin effective oxide thickness (EOT  $\sim$ 1.4nm for the RTA950°C sample) and superior properties. Based on the experimental results, the rapid thermal annealing can effectively improve the reliability and quality of the cerium dielectric film owing to the elimination of traps in the dielectrics and interfacial layer between CeO<sub>2</sub>/Si. In addition, the cerium dioxide has excellent thermal stability on Si substrate and high temperature to crystallize. The cerium dioxide with post-deposition rapid thermal annealing is a potential candidate for the future ultra-large scale integrated circuit (ULSI) applications.

#### I. INTRODUCTION

Recently, many high dielectric constant (high-k) materials like Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, and HfO<sub>2</sub> [1]-[4] have been widely studied to replace the silicon dioxide owing to the inevitability of its high leakage as the thickness scales down. Gate dielectric materials with a high dielectric constant, a low interface state density and a good thermal stability appear to be promising for next generation gate dielectric applications. Moreover, materials with too lower or too higher dielectric constant may not be adequate choice for alternative gate dielectric application. Ultra high-k materials such as STO or BST may cause fringing field induced barrier lowing effect [5]. And materials having relatively low dielectric constant such as Al<sub>2</sub>O<sub>3</sub> and Y<sub>2</sub>O<sub>3</sub> do not provide sufficient advantages over SiO2 or Si3N4 [6]. Cerium dioxide (CeO<sub>2</sub>), which has been extensively researched for its use as a buffer layer for YBa<sub>2</sub>Cu<sub>3</sub>O<sub>(7-x)</sub> (YBCO) on sapphire [7], a buried insulator for silicon-on-insulator (SOI) [8] and PbZrTiCeO<sub>3</sub> (PZT) ceramics [9], has lately been used as gate dielectric material [10]. Many superior properties of cerium dioxide, such as a lattice nearly matched to that of silicon (a=0.5411nm) and a sufficiently high dielectric constant (~26) ensure its high thermal stability on silicon and high scaling capacity. In this study, the electrical and physical characteristics of ultra-thin cerium dielectrics with

rapid thermal annealing are investigated.

#### **II. EXPERIMENT**

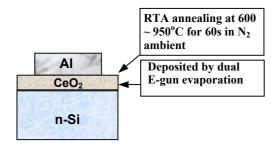

Al/CeO<sub>2</sub>/n-Si capacitors of an area of 6.36×10<sup>-5</sup>  $cm^2$  were fabricated on 4 inch n-type (100)-oriented Si wafers. Figure 1 shows key process flows of cerium dielectrics with post-deposition anneal (PDA). All samples were first cleaned by a standard Radio Corporation of America clean. The CeO<sub>2</sub> film was then deposited by electron beam evaporation. After the gate dielectric had been formed, the samples were treated by rapid thermal anneal (RTA) at 600  $\sim$ 950°C for 60s in N<sub>2</sub> ambient. Then, a 5000 Å Al film was deposited on the  $CeO_2$  film by a thermal coater. After that, the gate of the capacitor was defined lithographically and etched. Finally, a 5000 Å Al film was also deposited on the backside of the wafer to form the ohmic contact. There may be an interfacial oxide layer between CeO2 and Si. Therefore, the barrier parameters to be discussed in this paper are

"effective" values that include the effects of these interfacial layers. The effective oxide thickness (EOT) was estimated by the high frequency (0.1 MHz) capacitance versus voltage (C-V) curve in the strong accumulation region without considering quantum mechanical effects. The electrical properties were measured by using an HP 4156B semiconductor parameter analyzer and an HP4284A precision LCR meter.

# **III. RESULTS AND DISCUSSION**

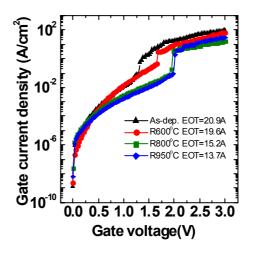

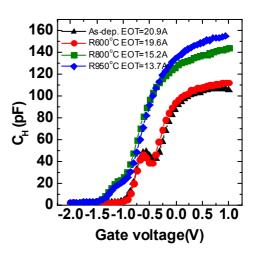

Figure 2 shows the J-E characteristics of these samples. The breakdown electric field becomes larger and the leakage current density decreases as the annealing temperature increases. It should be noted that CeO<sub>2</sub> still has excellent electrical performance, even through the high temperature annealing up to 950°C. It is seemed that the CeO<sub>2</sub> film does not crystallized after high temperature RTA treatment. Figure 3 shows the high frequency (0.1MHz) capacitance versus gate voltage (C-V) characteristics of cerium dielectrics with rapid thermal annealing at different annealing temperature. We can see that as the annealing temperature increases, the EOT decreases simultaneously. High temperature annealing can densify the CeO<sub>2</sub> film and make the dielectrics more stoichiometric. Besides, there are some distortions for the as-deposited sample and the sample with RTA at  $600^{\circ}$ C. We believe that it is owing to the serious interface state (fast traps) at the CeO<sub>2</sub>/Si substrate interface [11]. Ultra high temperature annealing may help to improve this distortion.

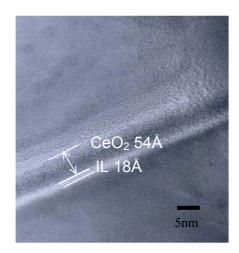

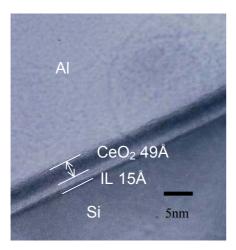

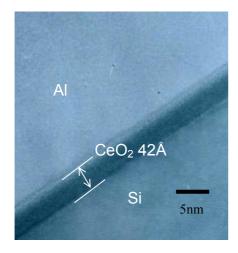

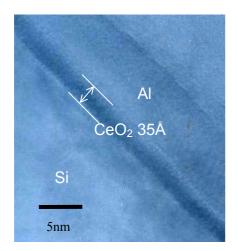

Figure 4~7 show the high resolution transmission electron microscopy (HRTEM) images of the cerium dioxide without treatment and with rapid thermal annealing at 600~950°C, respectively. For the TEM image of the as-deposited sample in Fig. 4, the physical thickness of the CeO<sub>2</sub> film is about 54 Å and obviously there is an interfacial layer (IL) about 18 Å existing between CeO2 and the Si substrate. From Fig.5 to Fig.7, we can find that as the annealing temperature increases, the thickness of the  $CeO_2$  film becomes thinner and densified. Besides, it is apparent that the interfacial layer thickness gradually decrease and finally almost disappear. Therefore, we can rationally suppose that the high temperature annealing can reduce the interfacial layer and improve the cerium dielectrics. The HRTEM results can explain the C-V characteristics of cerium dielectrics, as shown in Fig.3.

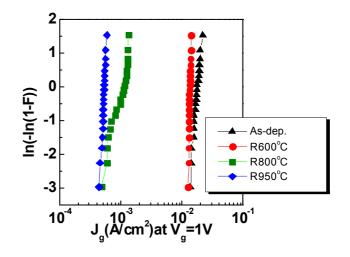

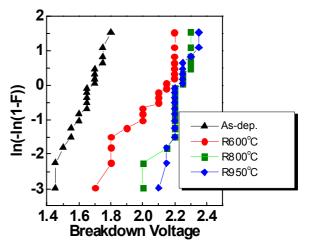

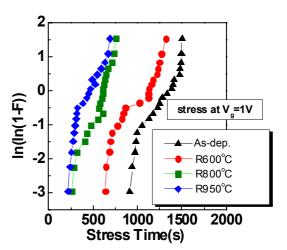

Figure 8 shows the Weibull plots of the leakage current density at V<sub>g</sub>=1V for the cerium dioxide treated by RTA at different temperature. We can observe the RTA treatment improves not only the leakage current density but also the distribution uniformity (Weibull slope). Figure 9 shows the Weibull plots of the dielectric breakdown voltage for the samples treated by RTA. As the RTA temperature increases, the breakdown voltage is raised form 1.4V to 2.3V. The Weibull plots of time to breakdown for the samples treated by RTA is presented in Figure 10.The samples are stressed at V<sub>g</sub>=1V. Obviously, the time-dependent dielectric breakdown (TDDB) is improved after high temperature RTA treatment. Furthermore, the RTA treatment can effectively improve the reliability of the cerium dielectric film owing to the elimination of traps in the dielectrics and interfacial layer between CeO<sub>2</sub>/Si.

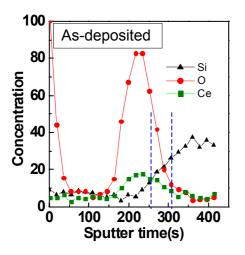

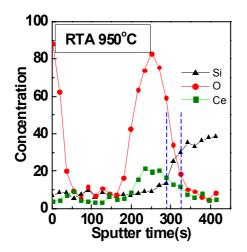

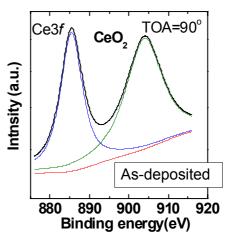

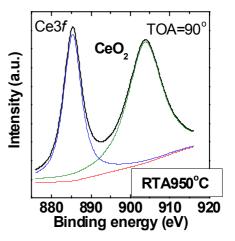

Figure 11~12 show the Auger electron spectrometer (AES) analysis of the as-deposited and RTA 950°C samples respectively. Form Fig.11, we can find the apparently interfacial layer between CeO<sub>2</sub> and Si substrate (marked in this figure). After the RTA 950°C treatment in Fig.12, the composition of CeO<sub>2</sub> film is still stable and the interfacial layer becomes smaller. Figure. 13~14 show the Ce3f electron spectroscopy for the chemical analysis (ESCA) spectra of the as-deposited and RTA 950°C samples. A take-off angle (TOA) of 90° was used to measure the ESCA spectra. The peaks of Ce-O bonding are respectively at 884 eV (Ce3d<sub>3/2</sub>) and 902 eV (Ce3 $d_{5/2}$ ). We can find the peaks and profiles of the as-deposited and RTA 950°C samples are almost the same. It means that any other bonding, especially

Ce-Si bonding, dose not formed in the cerium dielectrics after high temperature RTA treatment. Therefore, the cerium dielectric has excellent thermal stability on Si substrate.

# **IV. CONCLUSIONS**

In conclusion, we propose an ultra-thin cerium dioxide with post-deposition rapid thermal annealing, which exhibits the thin EOT (~1.4nm for the RTA950°C sample) and superior properties. Based on the experimental results, the rapid thermal annealing can effectively improve the reliability and quality of the cerium dioxide owing to the elimination of traps in the dielectrics and interfacial layer between CeO<sub>2</sub>/Si. Besides, the cerium dioxide has excellent thermal stability on Si substrate and high temperature to crystallize. Therefore, it can be the candidate for the future ultra-large scale integrated circuit (ULSI) applications.

### ACKNOWLEDGEMENT

The authors would like to thank the National Science Council of the Republic of China, Taiwan, for financially supporting this research under Contract No. NSC92-2215-E009-022. The National Nano Device Laboratory, R.O.C. is also appreciated for their technical assistance.

#### REFERENCES

- [1] J. Kolodzey, E. A. Chowdhury, T. N. Adam, Q. Guohua, I. Rau, J. O. Olowolafe, J. S. Suehle, and C. Yuan, "Electrical conduction and dielectric breakdown in aluminum oxide insulators on silicon," *IEEE Trans. on Electron Devices*, vol. 47, no. 1, pp. 121-128, Jan. 2000.

- [2] Yanjun Ma, Yoshi Ono, Lisa Stecker, David R. Evans, and S. T. Hsu, "Zirconium oxide based gate dielectrics with equivalent oxide thickness of less than 1.0 nm and performance of submicron MOSFET using a nitride gate replacement process," *in IEDM Tech. Dig.*, 1999, pp. 136-139.

- [3] C. Hobbs, H. Tseng, K. Reid, B. Taylor, L. Dip, L. Hebert, R. Garcia, R. Hegde, J. Grant, D. Gilmer, A. Franke, V. Dhandapani, M. Azrak, L. Prabhu, R. Rai, S. Bagchu, J. Conner, S. Backer, F. Dumbuya, B. Nguyen, and P. Tobin, "80 nm poly-Si gate CMOS with HfO<sub>2</sub> gate dielectric," *in IEDM Tech. Dig.*, 2001, pp. 30.1.1-30.1.4.

- [4] S. B. Samavedam, L. B. La, J. Smith, S. Dakshina-Murthy, E. Luckowski, J. Schaeffer, M. Zavala, R. Martin, V. Dhandapani, D. Triyoso, H. H. Tseng, P. J. Tobin, D. C. Gilmer, C. Hobbs, W. J. Taylor, J. M. Grant, R. I. Hegde, J. Mogab, C.

Thomas, P. Abramowitz, M. Moosa, J. Conner, J. Jiang, V. Arunachalam, M. Sadd, B-Y. Nguyen and B. White, "Dual-metal gate CMOS with HfO<sub>2</sub> gate dielectric," *in IEDM Tech. Dig.*, pp. 433-436, 2002.

- [5] B.Cheng et al, "The impact of high-/spl kappa/ gate dielectric and metal gate electrodes on sub-100nm MOSFETs", IEEE Tran. Electron Device, 46, 1537, (1999)

- [6] Laegu Kang et al, "Ultra thin Hanium Oxide with Low Leakage and Excellent Reliability for Alternative Gate Dielectric Application"IEDM Tech.Dig., p.633,1999

- [7] F. Wang, and R. Wordenweber, "Large-area epitaxial CeO<sub>2</sub> buffer layers on sapphire substrates for the growth high quality YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7</sub> films," *Thin Solid Films*, vol. 227, pp. 200-204, 1993.

- [8] C. A. Copetti, H. Soltner, J. Schubert, W. Zander, O. Hollricher, Ch. Buchal, H. Schulz, N. Tellman, and N. Klein, "High quality epitaxy of YBCO on silicon-on-sapphire with the multiple buffer layerYSZ/CeO<sub>2</sub>," *Appl. Phys. Lett.*, vol. 63, pp. 1429-1432, 1993.

- [9] J.-H. Yoo, Y.-W. Lee, S.-M. Hwang, H.-S. Yoon, H.-S. Jeong, J.-S. Kim, and C.-S. Yoo, "Piezoelectric properties of PNW-PMN-PZT ceramics for high power piezoelectric transformer," *in 2000 ISAF Symp. on Appl. of Ferro.*, vol. 1, pp. 495-498, 2001.

- [10]L. Tye, N. A. El-Masry, T. Chikyow, P. McLarty, and S. M. Bedair, "Electrical characteristics of epitaxial CeO<sub>2</sub> on Si(111)," *Appl. Phys. Lett.*, vol. 65, no. 24, pp. 3081-3083, 1994.

- [11]Ghetti, A.; Sangiorgi, E.; Bude, J.; Sorsch, T.W.; Weber, "Tunneling into interface states as reliability monitor for ultrathin oxides", *IEEE Trans. on Electron Devices*, Vol 47, pp: 2358 -2365, Dec. 2000

Fig.1 Key process flows of the fabrication for cerium dielectrics with post-deposition anneal (PDA).

Fig.2 The J-E characteristics of cerium dielectrics with RTA at different temperature.

Fig.3 The high frequency (100kHz) C-V characteristics of cerium dielectrics with RTA at different temperature.

Fig.4 The TEM image of the cerium dioxide without RTA treatment

Fig.5 The TEM image of the cerium dioxide with RTA 600°C.

Fig.6 The TEM image of the cerium dioxide with RTA 800°C.

Fig.7 The TEM image of the cerium dioxide with RTA  $950^{\circ}$ C.

Fig.8 Weibull plots of the leakage current density at  $V_g=1V$  for the samples treated by RTA.

Fig.9 Weibull plots of dielectric breakdown voltage for the samples treated by RTA.

Fig.10 Weibull plots of time to breakdown for the samples treated by RTA.

Fig.11 AES analysis of the as-deposited sample.

Fig.12 AES analysis of the sample treated by RTA 950°C.

Fig.13 Ce3*f* ESCA spectra of the as-deposited sample.

Fig.14 Ce3f ESCA spectra of the sample treated by RTA 950°C.