# Low Power Consumption Analog Matched Filter

MASAHIRO SASAKI<sup>1)</sup>, TAKEYASU SAKAI<sup>2)</sup>, TAKASHI MATSUMOTO<sup>1)</sup> <sup>1)</sup>Department of Electrical, Electronics and Computer Engineering Waseda University <sup>1)</sup>Graduate School of Science and Engineering, Waseda University <sup>2)</sup>Advanced Research Institute for Science and Engineering Waseda University 3-4-1 Ohkubo, Shinjuku-ku, Tokyo, 169-8555 JAPAN

*Abstract:* - A low power consumption AMF (Analog Matched Filter) is proposed which utilizes capacitor Multiply and capacitor Accumulation operations. High speed - high precision A/D converter is unnecessary because the proposed circuit directly samples received analog signal. The code shifting MF structure is used to prevent error from accumulating. A 15-tap AMF circuit was fabricated using CMOS process. Power consumption for 128-tap circuit is estimated as 2.35mW@25MHz 3.3V. The area is estimated as 1.6mm<sup>2</sup> so that the proposed circuit will be applicable LSI for mobile terminals.

*Key-Words:* - DS-CDMA, Matched Filter, Analog circuit, Weighted-sum operation, Spread spectrum, Multiply and Accumulation operation

### **1** Introduction

Recently, mobile terminals tend to adopt the DS-CDMA system. This system needs Matched Filters (MF) for aquisition of PN codes and various kinds of MF are realized, such as analog, CCD, SAW, as well as digital. Reduction of power consumption and chip area have been important issues in order that MF is applicable to mobile terminal LSI.

There is a great amount of demand for MF with respect to speed and number of taps, which naturally demand more power consumption and chip area.

In this paper, a low power consumption AMF (Analog Matched Filter) is proposed which utilizes capacitor Multiply and capacitor Accumulation operations. The proposed AMF circuit is designed and fabricated using 0.35 mm CMOS technology.

# 2 **Problem Description**

### 2.1 Matched Filter

To recover information signal, it is necessary to perform correlation operation on PN codes in the DS-CDMA system. The fundamental operation is described by

$$f(t) = \sum_{i=1}^{n} a(i) r(t-i)$$

(1)

Here, *n* is the number of taps, a(i) is a PN code and r(t) is a received signal.

This equation indicates that the peak correlation value results only when the timing of a PN code matches that of a received signal. A receiver restores the original information by the detected correlation timing.

### 2.2 Digital Matched Filter

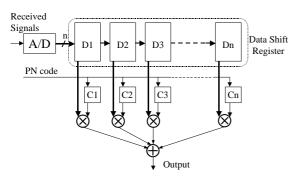

A block diagram of the conventional DMF (Digital Matched Filter) system is shown in Fig. 1 and Fig. 2.

#### 2.2.1 Data Shifting Matched Filter

Storing a received signal one by one in a data shift register (for received signals), this scheme outputs the correlation value operated with the PN code of each tap. This is an FIR filter where the number of taps is equal to the code length of a PN code. This structure is straightforward and general. However, power consumption becomes large since the data shift registers operate simultaneously.

If the number of quantization bits of an input signal increases, power consumption and chip area will increase further.

Fig. 1: Operation Block of Data shifting MF

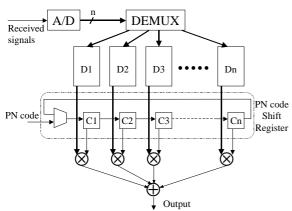

### 2.2.2 Code Shifting Matched Filter

This filter utilizes the code shift register (for PN codes) instead of the data shift register (for received signals) used in the data shifting MF. Moreover, a received signal is distributed to the register at every sampling. Consequently, it can reduce the power consumption.

Although power consumption of the DMF itself is reduced [1], high speed - high precision A/D converter is needed for quantizing a received signal with sufficient accuracy which naturally increases power consumption as well as chip area.

Fig. 2: Operation Block of Code shifting MF

#### 2.3 Analog Matched Filter

Analog MF in [2] [3] is proposed for this reason. The operation block of AMF is almost the same as a digital system. However, the A/D converter described before is unnecessary and low power consumption is realized by using a S/H (Sample-and-Hold) circuit instead of the shift register for received.

Error accumulates in the data shifting analog MF for every transmission so that it is difficult to form large number of taps. On the other hand, MF has an effective structure in an analog MF system since the

code shifting analog MF does not produce the error by transmission.

### **3 Problem Solution**

In this paper, a low power consumption AMF (Analog Matched Filter) which utilizes capacitor Multiply and capacitor Accumulation operations [4] is proposed.

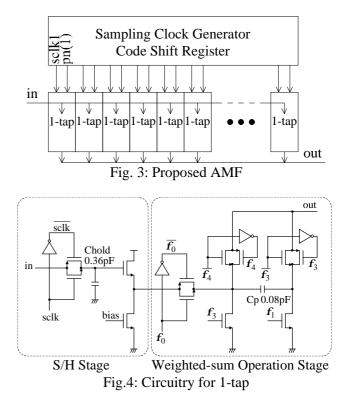

The proposed structure of the AMF is shown in Fig. 3, and circuitry for 1-tap is shown in Fig. 4.

Note that a straightforward weighted sum circuit with capacitors can operate on either positive voltages or on negative voltages. The proposed circuit can perform weighted sum operations on signed voltages by changing connection of capacitor nodes.

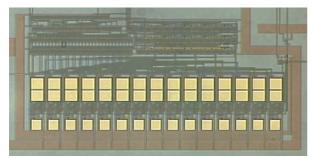

This proposal circuit for 15-tap was fabricated in a 0.35mm, 3 metal, 2 poly, 3.3V CMOS process. A chip microphotograph is shown in Fig.5 and Fig. 6.

The chip size of an AMF circuit area is about 0.2mm<sup>2</sup>, so that estimated area for 128-tap is approximately 1.6mm<sup>2</sup>. However, due to the restriction of design rule, capacitor that is an important component has to be designed between Poly-Metal in this chip. For this reason, the circuit area becomes large. By using the capacitor between

Poly-Poly, the chip area is significantly reducible, and the wiring capacitor can also be reduced, thus reduction of the power consumption is also expected.

Fig. 5: Microphotograph of the Analog Matched Filter

Fig. 6: Microphotograph of the circuitry for 1-tap

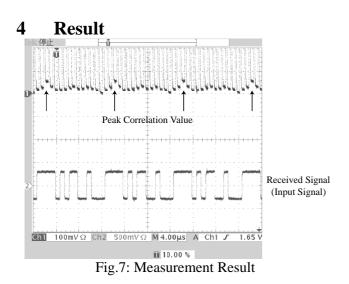

The measured waveform is shown in Fig. 7. The peak of a correlation value has appeared once for every 15 operations so that the MF is fully functional.

Comparison with other results is shown in Table 1. Although direct comparison cannot be performed due to difference of processes, this proposal circuit may serve as an effective system by smaller chip area and power consumption.

|                    | Core area            | Power                 | Technology      |

|--------------------|----------------------|-----------------------|-----------------|

| DMF <sub>[1]</sub> | 0.300mm <sup>2</sup> | 7.48mW<br>40MHz, 1.8V | 0.18 <b>m</b> m |

| AMF <sub>[2]</sub> | 91mm <sup>2</sup>    | 225mW<br>20MHz, 3.0V  | 0.8 <b>m</b> m  |

| Proposed<br>AMF    | 1.6mm <sup>2</sup>   | 2.35mW<br>25MHz, 3.3V | 0.35 <b>m</b> m |

Table 1: Comparison of Each Architecture

The feature of this proposal circuit is shown in Table 2.

Table 2: Features of the Proposed AMF

| Voltage           | 3.3V                              |  |

|-------------------|-----------------------------------|--|

| Power Consumption | 168 <b>m</b> W @1.25MHz           |  |

| Chip Area         | 0.2mm <sup>2</sup> (Circuit Area) |  |

| Number of Taps    | 15                                |  |

| Maximum chip rate | 25MHz                             |  |

| Process           | 0.35 <b>m</b> m                   |  |

## 5 Conclusion

A low power consumption AMF (Analog Matched Filter) is proposed which utilizes capacitor Multiply and capacitor Accumulation operations. High speed - high precision A/D converter is unnecessary because the proposed circuit directly samples received analog signal. The code shifting MF structure is used to prevent error from accumulating. A 15-tap AMF circuit was fabricated using CMOS process. Power consumption for 128-tap circuit is estimated as 2.35mW@25MHz 3.3V. The area is estimated as 1.6mm<sup>2</sup> so that the proposed circuit will be applicable LSI for mobile terminals.

Based on the measurement result, the 128-tap AMF using the capacitor between Poly-Poly is due to be designed.

### 6 Acknowledgement

The VLSI chip in this study has been fabricated in the chip fabrication program of VLSI Design and Education Center(VDEC), the University of Tokyo with the collaboration by Rohm Corporation and Toppan Printing Corporation.

#### References:

- K. Kitamura, K. Taki, T. Ogata, and Y. Murata, "Low Power Consumption CMOS Digital Matched Filter - An Application Example of the Plastic Hard Macro<sup>TM</sup> Technology", IPSJ JOURNAL Abstract, Vol.42, No.04 - 040, April 2001, pp. 219-224.

- [2] J. Chen, G. Shou, and C. Zhou, "High-Speed Low-Power Complex Matched Filter for W-CDMA: Algorithm and VLSI-Architecture", IEICE Trans. Fundamentals, VOL.E83-A, No.1, January 2000, pp. 150-157.

- [3] M. Sawahashi, F. Adachi, G. Shou, and C. Zhou, "Low-Power Consuming Analog-Type Matched Filter for DS-CDMA Mobile Radio", IEICE Trans. Fundamentals, VOL.E79-A, No.12, December 1996, pp. 2071-2077.

- [4] T. Sakai, H. Nagai, and T. Matsumoto, "Multi-Input Floating Gate Differential Amplifier and Applications to Intelligent Sensors", IEICE Trans. Fundamentals, VOL.E82-A, No.2, February 1999, pp. 335-340.