# **Frequency Synthesizer Based on Pulse Swallowing**

MILAN STORK

Dept. of Applied Electronics and Telecommunications/RICE Faculty of Electrical Engineering University of West Bohemia, Plzen,

Czech Republic

stork@kae.zcu.cz

*Abstract* - This article presents a design of new principle of the fractional frequency synthesizer based on pulse swallowing. This principle can be used for spurious phase modulation suppression when pulses are periodically removed from pulse train. The new synthesizer can be used also as a universal building block in phase locked loop frequency synthesizers. The mathematical analysis and simulations of the system are also presented.

*Key-Words* – comparator; fractional frequency synthesis; frequency divider; generator; lowpass filter; pulse removing; simulation

### **1** Introduction

The aim of frequency synthesis is to generate an arbitrary frequency from a given standard frequency or frequencies. Today, the frequency synthesizers are also an essential part of any modern transceiver system. They generate clock and oscillator signals needed for up and down conversion. The fine frequency resolution, low spurious signals, accuracy and stability are most important for these devices. The two most popular structures of radio-frequency synthesizers are the fractional-*N* frequency synthesizer and the integer-*N* frequency synthesizer.

Although fractional-N synthesizer owns a great performance in frequency resolution and settling time, its division number depends on accumulator carrier which may lead to spur noise closing to the wanted signal due to the periodically produced characteristic. Consequently, compared with the integer-N frequency synthesizer, a more complicated modulator is needed to alleviate the influence of noise for fractional - N synthesizer [1 - 7].

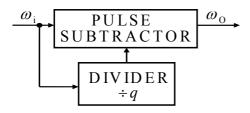

Fig. 1. The block diagram of pulse swallowing. Each *q*-th pulse is removed.

One of the simplest solutions for generating desired frequency from reference frequency is pulse-swallowing integer-*N* frequency synthesizer

(see Fig. 1). Suppose a pulse train in which pulses are placed in regular distances  $T_i$  (frequency  $\omega_i$ ) on time axis. If we remove each q pulse, then one period is missing and phase undergoes a step change equal  $2\pi$ , that is,

$$\varphi(t) = \omega_i t - 2\pi V(t_k) \tag{1}$$

where  $V(t_k)$  is the step function occurring at instances

$$t_k = kqT_i \tag{2}$$

where  $k=\dots-1, 0, 1, 2, \dots$ , and the average frequency  $\omega_0$  may be expressed as

$$\omega_o = \omega_i \frac{q-1}{q} \tag{3}$$

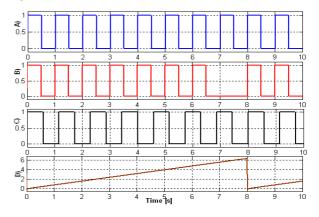

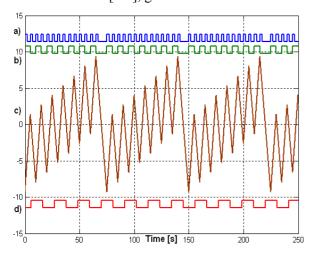

The simulation of input pulses, pulse omission of each  $8^{\text{th}}$  pulse (q=8), equally distributed output pulses and spurious phase modulation is shown in Fig. 2. [8, 9, 10].

Fig. 2. Pulse swallowing principle. A) input pulses,B) pulse omission of each 8th pulse (q=8), C)equally distributed output pulses and D) spuriousphase modulation.

Fig. 3. The time diagram of sine wave signals for calculation of frequency spectrum. A) input,  $f_i=1$  Hz B) one period omission of each 8th pulse (q=8), C) desired sine wave signal  $f_0=0.875$  Hz according (3) and D) spurious phase modulation.

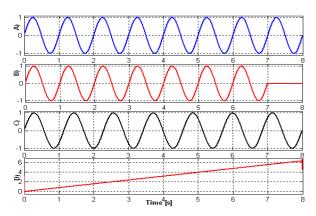

For frequency spectrum calculation, the sine wave signals were used (see Fig. 3). The frequency spectrum of signal with period omission (q=8) and continuous sine wave signal with desired frequency  $f_0=0.875$  Hz is shown in Fig. 4.

Fig. 4. The frequency spectrum of period swallowing (each 8-th period), top and spectrum of continuous sine wave signal  $f_0$ =0.875 Hz, shifted bottom.

The frequency spectrum has bad spectral purity and therefore new frequency synthesizer was developed.

### **2** Frequency synthesizer principle

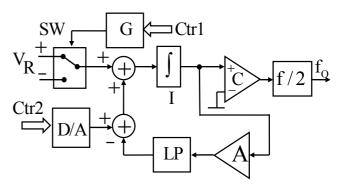

The block diagram of fractional frequency synthesizer is presented in Fig. 5. Suppose, that synthesizer is controlled by microcontroller by Ctr1 (control of pulse swallowing) and Ctr2, calculated average value of signal from generator G. Other parts are SW - switch,  $V_{\rm R}$  - reference voltage, Ctr2 - average value of signal with periodic pulse omission, I - integrator, A - amplifier, LP - low-pass filter, C - comparator, f/2 - frequency divider,  $f_{\rm O}$  - output frequency.

Fig. 5. The block diagram of fractional frequency synthesizer. Ctr1 - pulse swallowing control, G generator with pulse swallowing possibility, SW switch, Vr - reference voltage, Ctr2 - average value of signal with periodic pulse omission, I - integrator, A - amplifier, LP - low-pass filter, C - comparator,

f/2 - frequency divider,  $f_0$  - output frequency.

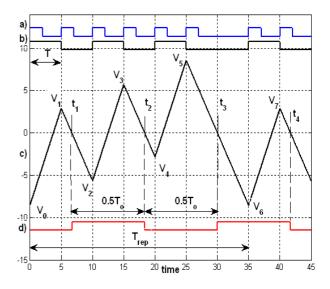

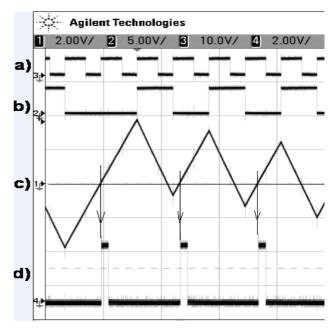

Fig. 6. The time diagram of signals in fractional frequency synthesizer based on pulse swallowing and charge balancing. a) Generator clock signal with pulse omission possibility, period *T*, b) signal a) divided by 2, c) integrator output, d) output signal  $f_0$ .  $T_{rep}$  - repeated period, output period  $T_0$ .  $V_0 \div V_7$  voltage on integrator output,  $t_1 \div t_4$  times of integrator voltage leading edge zero crossing.

The synthesizer output signal is derived according example presented in Fig. 6. for  $V_{\rm R} = \pm 2$ V and initial integrator voltage  $V_0$ . Suppose, that we have input signal (with period T = 5) with omission every 7<sup>th</sup> pulse (pulse is deleted in time t = 30, signal a) in Fig. 6). The number of pulses without omission pulses is  $N_{\rm P}$  and number of deleted pulses is  $D_{\rm P}$ . The inverted mean voltage  $V_{\rm M}$  on the output of switch SW (for  $V_{\rm R} = \pm 2$  V) is given by eq. (4), for  $N_{\rm P} = 7$ and  $D_{\rm P} = 1$  (for signal b), Fig. 6)

$$V_{M} = V_{R} \frac{D_{P}T}{N_{P}T} = V_{R} \frac{D_{P}}{N_{P}} = V_{R} \frac{1}{7} = \frac{V_{R}}{7} = \frac{2}{7} = 0.2857$$

(4)

The voltage  $V_{\rm M}$  is calculated by means of D/A converter and its digital value is Ctr2. The mean voltage  $V_{\rm M}$  on D/A output is added to voltage on output of the switch SW. Therefore for voltage + $V_{\rm R}$  the voltage slope on integrator output is

$$k_{+} = V_{R} + V_{M} \tag{5}$$

and for voltage  $-V_R$  the voltage slope is

$$k_{-} = -V_{R} + V_{M} \tag{6}$$

)

Integrator output voltages  $V_1 \div V_6$  are given by

$$V_{1} = V_{0} + k_{+}T = V_{0} + (V_{R} + V_{M})T$$

$$V_{2} = V_{1} + k_{-}T = V_{1} + (-V_{R} + V_{M})T = V_{0} + 2V_{M}T$$

$$V_{3} = V_{2} + (V_{R} + V_{M})T = V_{0} + 3V_{M}T + V_{R}T$$

$$V_{4} = V_{3} + (-V_{R} + V_{M})T = V_{0} + 4V_{M}T$$

$$V_{5} = V_{4} + (V_{R} + V_{M})T = V_{0} + 5V_{M}T + V_{R}T$$

$$V_{6} = V_{5} + (-V_{R} + V_{M})2T$$

$$= V_{0} + (5V_{M} + V_{R} - 2V_{R} + 2V_{M})T$$

$$= V_{0} + (7V_{M} - V_{R})T$$

$$= V_{0} + (7V_{M} - V_{R})T = V_{0} + (7\frac{U_{R}}{7} - V_{R})T = V_{0}$$

$$(7)$$

From the eq. (7) can be calculated that  $V_6 = V_0$ ,  $V_7 = V_1$ ..., all is repeated periodically. The maximal voltage on integrator output is

$$\Delta V_{MAX} = V_5 - V_6 = V_5 - V_0 = V_0 + (5V_M + V_R)T - V_0$$

$$= (5V_M + V_R)T$$

(8)

and for  $V_{\rm M} = V_{\rm R}/7$  according (4).

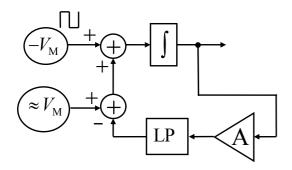

Fig. 7. The equivalent feedback loop of synthesizer.  $-V_{\rm M}$  mean value of pulsed voltage on switch output,  $\approx V_{\rm M}$  dc voltage from D/A converter, LP low pass filter, A amplifier.

The feedback loop consists of amplifier with gain *A* and low-pass filter LP. The loop holds zero average value on integrator output, see equivalent circuit in Fig. 7 (feedback loop balance some inaccuracy and differences between  $-V_{\rm M}$  and  $\approx V_{\rm M}$ ). Time  $t_1$  (Fig. 6) can be determined when cross zero voltage of line from  $V_1$  to  $V_2$ , where  $V_1$  is

$$V_{1} = V_{0} + k_{+}T = V_{0} + (V_{R} + V_{M})T$$

$$= \left(-\frac{6}{7}V_{R} + V_{R} + \frac{V_{R}}{7}\right)T = \frac{2}{7}V_{R}T$$

(9)

and after some manipulation

$$t_1 = T + \frac{T}{3} \tag{10}$$

and similarly  $t_2$  and  $t_3$  (Fig. 6)

$$t_2 = 3T + \frac{2T}{3}$$

(11)

$$t_3 = 5T + T = 6T$$

(12)

and first half output period  $0.5T_{\rm O}$  is

$$0.5T_o = t_2 - t_1 = 3T + \frac{2T}{3} - \left(T + \frac{T}{3}\right) = \frac{7}{3}T \quad (13)$$

and second half output period  $0.5T_{\rm O}$  is

$$0.5T_o = t_3 - t_2 = 6T - \left(3T + \frac{2T}{3}\right) = \frac{7}{3}T \qquad (14)$$

From eq. (13) and (14), frequency synthesizer output frequency is derived

$$f_o = \frac{1}{T_o} = \frac{1}{0.5T_o + 0.5T_o} = \frac{1}{\left(\frac{7}{3} + \frac{7}{3}\right)T} = \frac{3}{14T}$$

$$= \frac{3}{14} f_{CLK} = \frac{3}{14} \left(\frac{1}{5}\right) = 0.042857$$

(15)

where is  $f_{\text{CLK}}$  generator frequency ( $f_{\text{CLK}} = 1/T = 0.2$  in this example). From previous results the output frequency  $f_0$  can be derived

$$f_{O} = \frac{1}{4} \left( \frac{N_{P} - D_{P}}{N_{P}} \right) \frac{1}{T} = \frac{1}{4} \left( \frac{N_{P} - D_{P}}{N_{P}} \right) f_{CLK} \quad (16)$$

and for  $N_P = 7$ ,  $D_P = 1$  and  $f_{CLK} = 0.2$  Hz, the  $f_O$  is

$$f_0 = (1/4) * [(7-1)/7] * 0.2 = 0.042857$$

[Hz] (17)

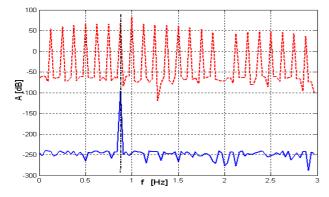

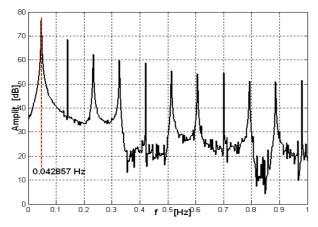

The frequency spectrum of square wave signal simulation according previous equations is presented in Fig. 8 (for  $N_{\rm P} = 7$ ,  $D_{\rm P} = 1$  and  $f_{\rm CLK}=0.2$  Hz, amplifier gain A = 0.0045 and

low-pass filter is 6<sup>th</sup> order Butterworth filter with corner frequency 0.04 [rad]), [11 - 15].

Fig. 8. The frequency spectrum of square-wave output signal of the synthesizer for  $N_{\rm P}$  = 7,  $D_{\rm P}$  = 1 and  $f_{\rm CLK}$ =0.2 Hz The amplifier gain is A=0.0045 and low-pass filter is 6<sup>th</sup> order Butterworth filter with corner frequency 0.04 [rad].

Fig. 9. The equivalent feedback loop for synthesizer stability evaluation.

## **3** Stability of the loop and filters

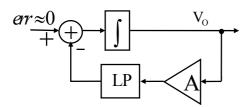

Because the synthesizer contain the feedback loop, it is important to solve stability. The simplified feedback loop is shown in Fig. 9. Input signal (err  $\approx$ 0) is difference of the mean value  $-V_{\rm M}$  (switch output) and  $\approx V_{\rm M}$  (D/A converter output). The closed feedback loop can be described by transfer function

$$\frac{V_o}{err} = \frac{\frac{1}{s}}{1 + \frac{1}{s}AF_{LP}(s)} = \frac{1}{s + A\frac{N(s)}{D(s)}}$$

(18)

$$= \frac{D(s)}{sD(s) + AN(s)}$$

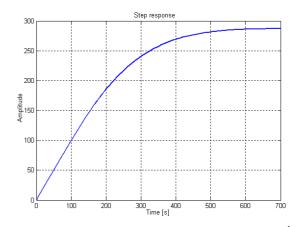

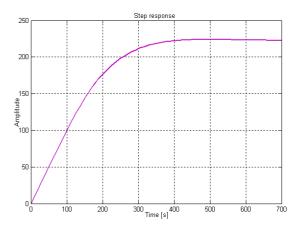

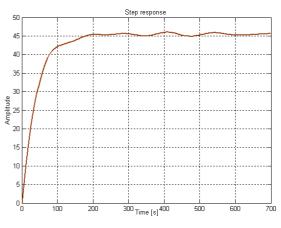

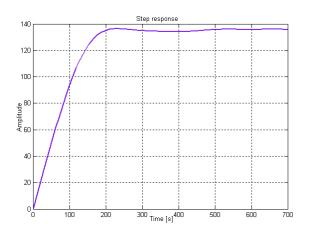

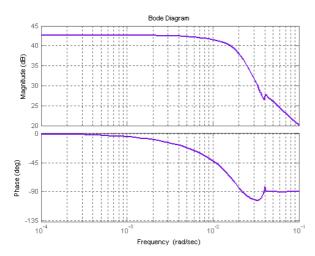

where N(s) and D(s) are numerator and denominator of low-pass filter transfer function respectively and A is value of amplifier gain. For system stability the real parts of the roots of closed loop denominator must be negative. The stability and behavior of the closed loop is controlled by gain A of the amplifier. The step response of closed loop for amplifier gain A and several types of 6<sup>th</sup> order low-pass filters (Bessel, Butterworth, Chebyshev and elliptic) with corner frequency 0.04 [rad] are presented in Fig. 10-13 and bode diagram for closed loop with elliptic filter in Fig. 14.

Fig. 10. Closed loop step response for Bessel  $6^{th}$  order analog filter with corner frequency 0.04 [rad], gain A = 0.0035

Fig. 11. Closed loop step response for Butterworth  $6^{\text{th}}$  order analog filter with corner frequency 0.04 [rad], gain A= 0.0045.

Fig. 12. Closed loop step response for Chebyshev type2,  $6^{\text{th}}$  order analog filter with corner frequency 0.04 [rad], gain A=0.022.

1

Fig. 13. Closed loop step response for elliptic 6<sup>th</sup> order analog filter with corner frequency 0.04 [rad], gain A = 0.0078

Fig. 14. The Bode diagram of closed loop for elliptic 6<sup>th</sup> order analog filter with corner frequency 0.04 [rad], gain A = 0.0078

Fig. 15. The time diagram of signals in fractional frequency synthesizer based on pulse swallowing and charge balancing. a) Generator clock signal with pulse omission, b) signal a) divided by 2,

c) integrator output, d) output signal  $f_0 = 0.04666$ [Hz], for  $N_{\rm P}$  = 15,  $D_{\rm P}$  = 1 and  $f_{\rm CLK}$  = 0.2 Hz.

The state space description of closed loop system is described as

$$\dot{x} = Ax + Bu; \quad y = Cx + D \tag{19}$$

where numerical values of matrices A, B, C, D (for 7<sup>th</sup> order system according Fig. 9 with 6<sup>th</sup> order elliptic filter) are

$$A = 10^{-2} \begin{bmatrix} -4.56 & -3.27 & -0.85 & -0.5 & -0.33 & -0.32 & -0.6 \\ 12.5 & 0 & 0 & 0 & 0 & 0 \\ 0 & 12.5 & 0 & 0 & 0 & 0 \\ 0 & 0 & 6.25 & 0 & 0 & 0 \\ 0 & 0 & 0 & 3.125 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1.56 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0.4 & 0 \end{bmatrix}$$

$$B = \begin{bmatrix} 2 & 0 & 0 & 0 & 0 \end{bmatrix}^{T}$$

(20)

$$C = 10^{-2} \begin{bmatrix} 50 & 18 & 13 & 6.6 & 8 & 9.3 & 41 \end{bmatrix}; D = \begin{bmatrix} 0 \end{bmatrix}$$

The zero-pole-gain of closed loop system  $(F_{CL})$ described by eq. (19) and (20) is

$$F_{CL}(s) = k_{CL} \frac{(s - z_1)(s - z_2) \cdots (s - z_6)}{(s - p_1)(s - p_2) \cdots (s - p_7)}$$

(21)

where  $k_{\rm CL}$ =1 and zero-pole values are:

$$z_{1,2} = -0.0008 \pm 0.0402i$$

$$z_{3,4} = -0.0049 \pm 0.0370i$$

$$z_{5,6} = -0.0170 \pm 0.0197i$$

$$p_{1,2} = -0.0008 \pm 0.0403i$$

$$p_{3,4} = -0.0059 \pm 0.0366i$$

$$p_{5,6} = -0.0095 \pm 0.0171i$$

$$p_{7} = -0.0131$$

$$zeros$$

$$z_{5,6} = -0.0095 \pm 0.0171i$$

# **4** Frequency synthesizer simulations

The simulation result was derived for  $N_{\rm P} = 15$ ,  $D_{\rm P} =$ 1 and  $f_{\text{CLK}}$ =0.2 Hz, amplifier gain A=0.0078 and 6<sup>th</sup> order elliptic low-pass filter with corner frequency 0.04 [rad] (see closed loop response, Fig. 13). The output frequency, according (16) is

$$f_{O} = \frac{1}{4} \left( \frac{N_{P} - D_{P}}{N_{P}} \right) f_{CLK}$$

$$= \frac{1}{4} \left( \frac{15 - 1}{15} \right) 0.2 = 0.04666$$

(23)

Signal derived by simulation are displayed in Fig. 15. This figure shows input signal a), b) input signal divided by 2 (on rising edge), c) integrator output, d) output signal. All signals are displayed in steady state.

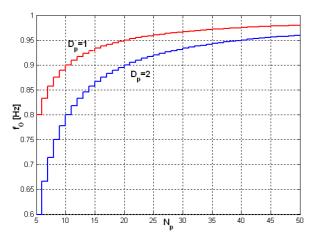

The relative output frequency  $f_0$  for  $f_{CLK}=4$ ,  $D_P=1$  and  $D_P=2$  and  $N_P=\langle 5:30 \rangle$  is presented in Fig. 16.

Fig. 15. Output frequency as function of  $N_P$  for  $f_{CLK}=4$ ,  $D_P=1$  and  $D_P=2$ .

Fig. 16. The time diagram of signals measured in frequency synthesizer. a) Input clock signal, b) signal with pulse omission (input clock frequency with pulse omission divided by 2),

c) integrator output, d) output signal f<sub>O</sub> = 3.7011 kHz, for N<sub>P</sub> = 13, D<sub>P</sub> = 1 and f<sub>CLK</sub>=8.0191 kHz.

### **5** Measurement results

The simplified (low frequency) version of pulse swallowing frequency synthesizer was constructed and measured. The result of measuring confirmed theory and simulations. The first example is shown in Fig. 16. It is important to note that inverting integrator was used and output signal frequency was not divided by 2, therefore equation for output frequency is given by

$$f_O = \frac{1}{2} \left( \frac{N_P - D_P}{N_P} \right) f_{CLK}$$

(24)

therefore for  $N_P = 13$ ,  $D_P = 1$  and  $f_{CLK}=8.0191$  kHz, the frequency of output pulses is  $f_O = 3.7011$  kHz.

Fig. 17. Zoom of Fig. 16. Principle of output signal generation – pulses on rising edge of signal c), crossing the zero level.

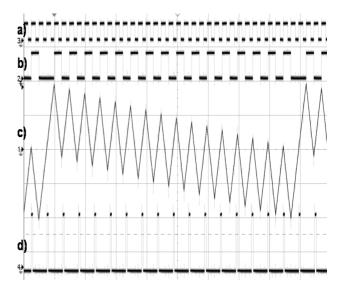

Fig. 18. The time diagram of signals measured in frequency synthesizer. a) Input clock signal, b) signal with pulse omission (input clock frequency with pulse omission divided by 2),

c) integrator output, d) output signal f<sub>0</sub> = 3.888 kHz, for N<sub>P</sub> = 33, D<sub>P</sub> = 1 and f<sub>CLK</sub>=8.0191 kHz.

The output signal (see Fig. 16 d) are generated when rising edge of integrator signal cross the zero level, all is displayed in Fig. 17.

The example for values  $N_{\rm P} = 33$ ,  $D_{\rm P} = 1$  and  $f_{\rm CLK}=8.0191$  kHz is shown in Fig. 18. Frequency of output signal, according eq. (24) is  $f_{\rm O} = 3.888$  kHz.

# **6** Conclusions

A detailed look at the concept of new fractional frequency synthesizer based on pulse omission technique and charge balancing has been presented in this paper. The new synthesizer can be also used as a universal building block in different types of frequency synthesizers (e.g. phase locked loops). The main advantage of this fractional synthesizer is simple generation of frequency. Analysis and simulation results of the new fractional synthesizer were also shown. The theory and simulation were confirmed by construction of synthesizer. The real signals were measured on this synthesizer.

# ACKNOWLEDGMENT

This research was supported by the European Regional Development Fund and Ministry of Education, Youth and Sports of the Czech Republic under project No. CZ.1.05/2.1.00/03.0094: Regional Innovation Centre for Electrical Engineering (RICE).

### References:

- [1] V. Manassewitch, Frequency synthesizers, 2nd ed. New York: Wiley, 1980.

- [2] U. L. Rohde, Microwave and wireless synthesizers: Theory and design. USA: John Wiley & Sons, Inc., 1997.

- [3] G. Goldberg, Digital techniques in frequency synthesis. New York: McGraw-Hill, 1995.

- [4] P. Sotiriadis, Diophantine frequency synthesis: A number theory approach to fine frequency synthesis. Miami: IEEE International Frequency Control Symposium, 2006.

- [5] P. Sotiriadis, Diophantine frequency synthesis. IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control Society, 53(11), 2006, pp. 1988–1998.

- [6] V. F. Kroupa, Close-to-the-carrier noise in DDFS. IEEE International Frequency Control Symposium, 1996, pp. 934–941.

- [7] V. F. Kroupa, Direct digital frequency synthesizers. New York: IEEE Reprint Press Book, 1998.

- [8] W. F. Egan, Frequency synthesis by phase lock, 2nd ed. New York: Wiley, 1999.

- [9] R. E. Best, Phase-locked loops: Design, simulation, and applications (5th ed.). New York: McGraw-Hill, 2003

- [10] J. L. Stensby, Phase-locked loops: Theory and applications. USA: CRC Press, 1997.

- [11] J. Vanakka, M. Waltari, K. Kosunen, & I. Halonen, A direct digital synthesizer with an on-chip D/A-converter. IEEE. Journal of Solid-State Circuits, 33(2), 1998, pp. 218–227. doi: 10.1109/4.658623.

- [12] W. F. Egan, Advanced Frequency synthesis by phase lock, 2nd ed. New York: Wiley, 2011.

- [13] M. Borkowski, T. Riley, J. Hakkinen and J. Kostamovaara, A practical  $\Delta$ - $\Sigma$  modulator design method based on periodical behavior analysis, IEEE Transaction on Circuits and Systems II: Express Briefs 52 (10) October, 2005, pp.626-630.

- [14] M. Kozak and I. Kale, Rigorous analysis of delta-sigma modulators for fractional-N PLL frequecy synthesis, IEEE Transaction on Circuits and Systems I: Regular Papers 51 (6) June, 2004, pp. 1148-1162.

- [15] T. Riley and J. Kostamovaara, A hybrid  $\Delta$ - $\Sigma$  fractional-N frequency synthesizer, IEEE Transaction on Circuits and Systems II: Analog and Digital Signal Processing 50 (4) April, 2003, pp. 835-844.