## **Logarithmic VU Meter Driver**

POSPISILIK MARTIN, ADAMEK MILAN

Faculty of Applied Informatics

Tomas Bata University in Zlin

Nam. T. G. Masaryka 5555, 760 01 Zlin

CZECH REPUBLIC

pospisilik@fai.utb.cz

Abstract: - This paper deals with a construction and practical testing of a VU meter driver that includes an accurate rectifier and logarithmic driver of a pointer-type gauge. The logarithm is taken from the rectified signal by employing a capacitor discharge voltage curve. In the first step, a simple rectifier and logarithmiser was designed and built in order to proof the theoretical premises. Then, based on the experience with this circuit, the more complex design of the VU meter driver was created.

Key-Words: - Audio signal rectifier, VU meter, gauge driver, logarithmiser

### 1 Introduction

Analog audio signal levels are often expressed in decibels compared to one reference level. Analog VU meters are usually equipped with a non-linear decibel scale which stem from the definition of a ratio unit [dB]. In this case only a simple front end rectifier is sufficient for a satisfactory level indication. However, it is more comfortable to take and display directly the logarithm of the voltage level of the signal because then one gain an advance of a linear gauge scale. In addition, the gauge range is usually extended to at least 30 dB.

There are several requirements that should be met by the accurate VU meter:

- Symmetrical processing of the AC signal voltage with low distortion observing the sufficient bandwidth,

- accurate measuring of the peak value (in audio systems there is usually a need to display peak values to prevent the signal from clipping the peaks),

- the peak value should be displayed for a period of time that is long enough so the user could clearly see it on the scale,

- the reaction time of the VU meter should be short enough so very short peaks could be displayed,

- it is convenient to take and display the logarithm of the measured value because of the typical character of the audio signal.

To meet these requirements, the advanced rectifier and driver for analog VU meter was designed and built.

## 2 Logarithm processing

The basic aim was to employ a quite simple method of processing a pulse-width modulation by a comparator-connected operational amplifier. The rectified signal is periodically compared to a reference voltage that can be described by the following equation:

$$u_{REF} = U_0 \cdot e^{-\frac{t - nT_0}{\tau}}; \qquad t \in \langle 0, T_0 \rangle; \ n \in \mathbf{N}$$

where  $U_0$  is the amplitude of the reference voltage [V], t is time flowing throughout the period  $T_0$  [s],  $T_0$  is a period of pulse width modulation [s], n is the order of the appropriate period [-] and  $\tau$  is a time constant defining the voltage slope [s].

To get the best resolution one need to obtain the highest possible amplitude of the reference voltage. Ideally,  $u_{REF}$  lies in the range between  $U_0 = U_{cc}$  at t = 0 and 0 at  $t = T_0$ . Practically, one will let the voltage to drop to 10 % of  $U_0$  which can be well implemented physically. Considering this level must be achieved in a period of  $T_0$ , one can determine the optimal value of  $\tau$ :

$$0.1 \cdot U_0 = U_0 e^{-\frac{T_0}{\tau}} \Rightarrow \tau = -\frac{T_0}{\ln(0.1)}$$

(2)

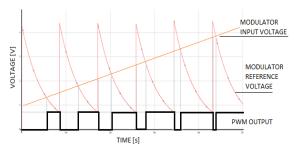

The behaviour of the signal is described in Fig 1. with a curve called "Modulator reference voltage". One can see that the slope of the voltage is exponential. Comparing this voltage to a direct voltage of a random level at the input of the modulator, the output of the modulator can be described with the following equation:

$$u_{OUT} = \begin{array}{c} \cdot & 0 \Leftrightarrow u_{IN} < u_{REF} \\ \cdot & U_{cc} \Leftrightarrow u_{IN} \ge u_{REF} \end{array}$$

(3)

where  $u_{OUT}$  is the output voltage of the ideal modulator [V],  $u_{IN}$  is the input voltage of the modulator [V],  $U_{cc}$  is the supply voltage of the ideal modulator [V],  $u_{REF}$  is the voltage described by equation (1) [V].

Fig. 1, PWM modulator waveforms

Considering a period of pulse width modulation  $T_0[s]$  and a period of time when the output of the modulator is in a high state ( $u_{OUT} = U_{cc}$ )  $t_H[s]$ , the ratio of the output signal of the modulator R can be simply described as:

$$R = \frac{t_H}{T_0} \tag{4}$$

In order to determine the value of R one must find such time t throughout the period of  $T_0$  in which  $u_{IN} = u_{REF}$ , because at this point lies the threshold of the comparator. Provided one consider invariable direct voltage at the input of the modulator, one can describe the dependence of R on  $u_{IN}$  (using equations 1, 2, 3, 4) as:

$$u_{IN} = const. = u_{REF} = U_0 \cdot e^{-\frac{t - nT_0}{\tau}}$$

(5)

$$t = -\frac{T_0}{\ln 0.1} \cdot \ln \left(\frac{u_{IN}}{U_0}\right); R = \frac{t}{T_0}$$

(6)

$$R = -\frac{1}{\ln 0.1} \cdot \ln \left( \frac{u_{IN}}{U_0} \right) \tag{7}$$

From the equation (7) one can see the logarithmic dependence of R on the input voltage  $u_{\rm IN}$ . Because the level of signal in [dB] is defined as Briggsian logarithm of the ratio between the measured and the reference level and the modulator, as deduced above, makes the Napierian logarithm, one need to recalculate the output of the modulator so as to order the proper scale was achieved. According to [1] one can use simple approximation:

$$\log x \approx 0.434\,294\,\cdot\ln x\tag{8}$$

The behavior of a PWM modulator with a reference voltage according to (1) can be seen in Fig. 1. There are two input voltages (modulator

input voltage and modulator reference voltage) and the appropriate output of the modulator displayed.

At the output of the modulator one get two-state signal with the ratio R. Throughout the period  $T_0$  this signal can be expressed with the aid of the Heaviside step function:

$$u_{OUT} = U_{cc} \cdot H(t - (1 - R)T_0); \quad t \in (0, T_0)$$

(9)

Integrating this signal in time, direct voltage corresponding to R can be got. One can express the mean value with the successive equation:

$$U_{MEAN} = \frac{1}{T_0} \int_0^{T_0} u_{OUT} dt = \frac{1}{T_0} \int_0^{T_0} U_{cc} \cdot H(t - (1 - R)T_0) dt = \frac{1}{T_0} \left( \int_0^{(1-R)T_0} 0 dt + \int_{(1-R)T_0}^{T_0} U_{cc} dt \right) = \frac{1}{T_0} \left( \left[ 0t \right]_0^{(1-R)T_0} + \left[ tU_{cc} \right]_{(1-R)T_0}^{T_0} \right) = \frac{1}{T_0} (T_0 U_{cc} - (1 - R)T_0 U_{cc}) = R U_{cc}$$

$$(10)$$

## 3 Sample circuit construction

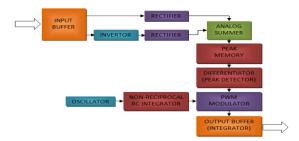

In order to proof the above mentioned theory a simple driver was built. Its basic blocks can be seen in Fig. 2.

Fig. 2, Basic blocks of the sample rectifier and logarithmic driver

At the input of the circuit, there is an input buffer that accommodates this circuit to preceding circuits in terms of the voltage level and the impedance of the signal. As there are two rectifiers employed in the circuit in order to improve the symmetry of either positive or the negative half-wave of the signal, one of the rectifiers must be front-ended with an inverter. Outputs of both rectifiers are then summarized by an analog summer and a simple peak memory. These blocks are simply based on a larger capacitor. The differentiator derivates the voltage on the peak memory capacitor in time and when a steep voltage peak occurs, it generates a short pulse that is added to the voltage on the memory capacitor. This improves the response of the pointer of the gauge as it is pushed by a high

current pulse. The proper response of the differentiator must be identified by a practical experiment with an appropriate gauge so the pointer does not overshoot the proper position. Now one come to the modulator which is based on a comparator that processes two signals – the voltage of the peak memory capacitor with a short pulse eventually added by the differentiator and the exponential voltage decay generated by a nonreciprocal RC integrator according to equation (1). The oscillator generates periodic pulses that are used to charge the integrator capacitor very fast while the discharge of the capacitor is executed slowly. The output buffer integrates the output voltage according to equation (10) and drives the scale.

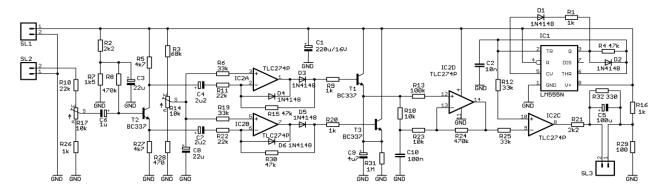

The schematics of the circuit can be seen in Fig. 3. There are three pin terminals in the circuit. These terminals are marked SL1 to SL3. SL1 serves to connect the power supply of 6.3 V. The pointer-type gauge is connected to SL3 and at SL2 there is the input of the driver.

#### 3.1 Input buffer and inverter

The input buffer and the inverter are both implemented by T2 transistor. Its operating point is set by resistors R2 and R7. Their values were set according to simulation of the circuit so the output amplitudes of the inverted and non-inverted outputs were clipped at equal levels – an optimal bias was found to be set at approx. 40 % of the supply voltage. The bias voltage is blocked by the capacitor C3. The level of the input signal can be adjusted by the rotary trimming resistor R17. The signal level behind the trimming resistor R17 is supposed to be around 0.3 V<sub>ef</sub> for the pointer displacement of 0 dB (80 % of the whole scale). The guiescent current through the transistor T2 is supposed to be around 450 μA. At the collector of T2 one get the signal with 180° phase shift while at the emitter of the

same transistor one get the signal with no phase shift. Collector and emitter resistors R5 and R27 are of equal value so the transistor works with a negative feedback of 100 %. Provided the outputs of input buffer / inverter are loaded with high impedance, the signal amplitudes at both outputs should be almost identical.

# 3.2 Symmetrical rectifiers and peak memory capacitor

There are two rectifiers in the circuit, based on operational amplifiers IC2A and IC2B. This is to improve the symmetry of the rectifier at high frequencies at which reverse recovery times of the diodes and limited slew rate of the operational amplifiers may take effect. The circuit was a subject of software simulations together with the input buffer and inverter and analog summer and the results acknowledged better linearity of AC to peak DC conversion at high frequencies and low amplitudes. Decoupling of rectifier inputs is realized with the aid of C4 and C7 capacitors. Each of both operational amplifiers is connected in the way of inverting amplifier for a negative half-wave with a gain of approximately 6 dB while for the positive half-waves the outputs of operational amplifiers are blocked by D3 and D5 diodes and their negative feedback is ensured by D4 and D6 diodes so the amplifiers are protected from deep negative saturation. The outputs of these operational amplifiers are fortified by T1 and T3 transistors that deliver the sufficient amount of current to charge the memory capacitor C9 to the proper peak value in a short time. Practically, some low bias is needed to set the optimal working points of the operational amplifiers and transistors. This bias is set by the rotary trimming resistor R14 in such a way that the quiescent voltage at C9 capacitor lies between 0.25 and 0.4 V. Successive blocks like differentiator and PWM modulator also take advantage of this bias.

Fig. 3, Sample circuit schematics

The outer effect of setting the bias is that the pointer of the gauge remains at the bottom of the scale when the driver is not excited. The value of the peak memory capacitor C9 is selected in order to ensure the charging time is fast enough while the discharge takes approximately 7.5 s.

#### 3.3 Differentiator

The differentiator is based on the IC2D operational amplifier. At first glance it seems it is connected similarly to the differential amplifier. Considering just the IC2D operational amplifier with resistors R13, R23 and R24 and that there are two inputs of the circuit, IN+ and IN-, both on the sides of the resistor R18, which is for our purposes omitted now, its output voltage can be loosely expressed like:

$$U_{OUT_{IC2D}} \cong U_{IN}^+ \left(\frac{R_{24} + R_{23}}{R_{23}}\right) - U_{IN}^- \frac{R_{24}}{R_{23}}$$

(11)

Neglecting the influence of the resistors R13 and R18 and the capacitor C10, one find  $U_{IN}^+ = U_{IN}^- = U_{IN}$ . Thus, the amplification of the circuit can be expressed like:

$$A \cong \frac{U_{OUT}_{IC2D}}{U_{IN}} \cong \frac{R_{24} + R_{23}}{R_{23}} - \frac{R_{24}}{R_{23}} = \frac{R_{23}}{R_{23}} = 1$$

(12)

Therefore, it is possible to state that for signals that change their voltage slow enough so there is no delay produced by the derivative element made of the resistor R18 and the capacitor C10, the amplification factor is close to 1. On the other hand if one suppose that the voltage at the input of the differentiator changed at a single jump from the value  $U_0$  to  $U_{PEAK}$ , the voltages  $U_{IN}^+$  and  $U_{IN}^-$  that can be found on both ends of the resistor R18 and the operational amplifier will be shortly driven to the positive saturation, producing a short high-level pulse.

# 3.4 PWM Modulator, reference signal generator and the output buffer

The PWM modulator is in fact very simple, consisting of the operational amplifier IC2C that compares the voltage at the output of the differentiator to the reference voltage. The principle of this operation has been described above. The reference voltage is generated right on the timing capacitor C2 that defines how the timer IC1 will oscillate as an astable circuit. Imagine that at the moment the driver is being turned on the capacitor C2 is discharged. TRIGGER voltage input (pin 2) of

the timer IC1 is lower than the trigger value and therefore the output of the timer (pin 3) will reach level H. The capacitor C2 is now rapidly charged through the diode D2. When its voltage exceeds <sup>2</sup>/<sub>3</sub> of the supply voltage, the THRESHOLD input of the timer (pin 6) will cause flipping the timer to the low output level. Now, the capacitor C2 discharges through the resistor R4. Because the CV input of the timer (pin 5) is now tied low to the timer output (pin 3) by the help of the diode D1 and the resistor R1, the voltage on the capacitor C2 must drop lower than to 1/3 of the supply voltage so the input TRIGGER drove the output of the timer high, leading to generate quasi-logarithmic voltage decay. It is not crucial how stable the capacity of the capacitor C2 is because its change affects only the period  $T_0$ , not the shape of the signal. The shape can be affected by leakage current through the capacitor and the inputs of the connected integrated circuits but in this case these influences can be neglected. The output buffer consists of the resistors R21, R32 and the capacitor C5. The values of R32 and C5 were found by practical tests with the particular gauge. They both damp overshoots of the pointer down. A voltage divider made of resistors R16 and R29 serves to bias the gauge so the influence of the bias set by the trimming resistor R14 is neutralized.

#### 4 Results

The above described circuit was built and underwent several tests the results of which are discussed below. The pointer-type gauge according to specification in Tab. 4 was connected and the circuit was supplied with 6.3 V (as acknowledged above). The air temperature was 20 °C. The input of the circuit was driven by an accurate programmable function generator. The sensitivity was set by the resistor R17 so that at 1 V RMS @ 1 kHz sinusoidal signal the pointer of the gauge stayed at 80 % of the scale (at this point typically 0 dB mark occurs on the scales). The bias was set by the resistor R14 so that pointer indicated 0 % of the scale when no signal was fed into the circuit input.

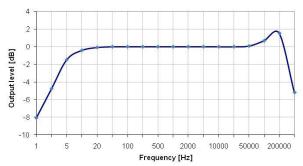

### 4.1 Rectifier frequency response

The frequency of the sinusoidal signal was changed from 1 Hz to 500 kHz at 1 V RMS and the corresponding voltage was measured by a digital voltmeter at the output of the operational amplifier IC2D (in front of the PWM modulator). Output signal level was expressed in dB compared to the

level of the input signal and the results were plotted on the Fig. 4.

Fig. 4, Rectifier frequency response

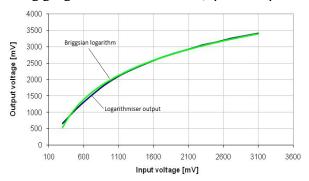

### 4.2 Logarithmiser performance

In this step it was tested how accurate is the logarithm taken from the rectified signal by the logarithmical PWM modulator. The input of the circuit was fed by sinusoidal signal at the frequency of 1 kHz. An RMS voltage was measured at the clamps of the analog gauge by a digital oscilloscope so that the non-linearity of the gauge was extruded. The results were plotted into a diagram to be seen in Fig. 5. As a nominal value of 0 dB, the level of 1.55 V RMS was set and the input voltage was changed from 0.15 V (- 20 dB) to 3.1 V (+ 6 dB). The input voltage is shown at the x-axis while at the y-axis there one can see the output voltage measured at the

analog gauge clamps. There are two curves in the diagram. The proper Briggsian logarithm is represented by the green line while the output of the logarithmic PWM modulator is represented by the blue line. As can be seen, at high levels both curves are almost identical while at low levels the blue curve becomes quite linear although the difference from the proper logarithm is, if the linearity of the analog gauge is taken into account, quite acceptable.

Fig. 5, Logarithmiser performance

## **5 Contemporary development**

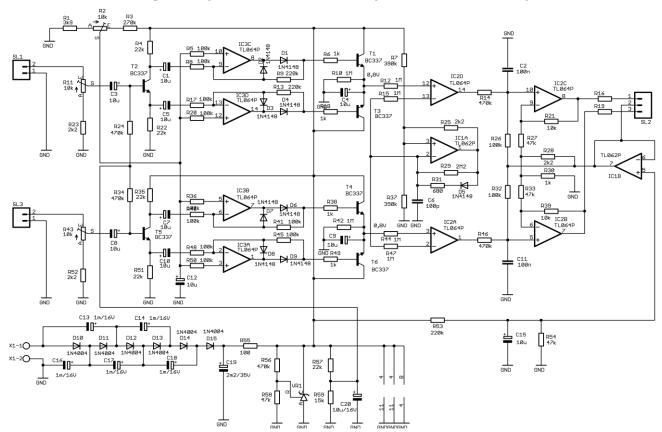

Based on the positive experience gained by practical tests on the circuit shown in Fig. 3, more complex rectifier and driver has been designed. Its circuit diagram can be seen in Fig. 6. The circuit is 2-

Fig. 6, Complex two-channel VU meters driver

channel with the inputs at the connectors SL1 and SL3. Analog VU meters are to be connected to the connector SL2. The circuit can be supplied with 6 V AC current, because it is supposed to be utilized in a vacuum-tube amplifier. The power supply is connected to the clamps X1 and a simple multiplier made of capacitors and diodes boosts the voltage to approximately 30 V. Then the parametric voltage regulator VR1 stabilises the voltage to 26 V. Increasing the supply voltage helps us to produce smoother and more accurate reference signal (see Fig. 1).

The construction of the input buffer and the rectifiers stayed unchanged, as well as the memory capacitor excitation. The 555 timer has been replaced with the operational amplifier IC1A that is connected as a stable trigger circuit. According to simulations this trigger circuit should run at 280 Hz. The quasi-logarithmic reference signal is generated at the capacitor C6. The comparators made with the operational amplifiers IC2A and IC2D share it. Another approach was employed at gauge peak reaction. At the output of the PWM modulators there are integrators R14/C2 and R46/C11. The gauges are excited via the operational amplifiers IC2C and IC2B. The values of the resistors R16 and R19 should be as low as possible. Then the gauge systems are damped heavily because of the low output impedance of the operational amplifiers with the appropriate feedback loops. The operational amplifier IC1B delivers bias voltage to the gauges. The bias of both channels is to be set by the rotary trimming resistor R2.

At the present time this circuit is a subject to debugging.

#### 6 Conclusion

In this paper a method of hardware signal logarithm processing was proposed. According to the above presented theory a simple logarithmical rectifier and driver was built in order to prove the theoretical premises.

The main advantages of this construction are as follows: symmetrical proceeding of the input signal, almost ideal frequency response at audible frequencies, logarithmical voltage output and improved gauge response at steep pulses.

Based on the experience gained at this circuit, more complex two-channel VU meter driver (see Fig. 6) was designed and is a subject to debugging at the present time.

## Acknowledgements

The project is supported by the European Regional Development Fund under the project CEBIA-Tech No. CZ.1.05/2.1.00/03.0089.

#### References:

- [1] X1. K. Rektorys et al., *Prehled uzite matematiky I.* Vyd. 6. Praha: Prometheus, 1995. 720 p. ISBN 80-85849-92-5.

- [2] X2. J. Puncochar., *Operacni zesilovace v elektronice*. Vyd. 5. Praha: BEN, 2002. 496 p. ISBN 80-7300-059-8.

- [3] X3. V. Zahlava, *Metodika navrhu plosnych spoju*. Czech Technical University in Prague, 2000

- [4] X4. P. Bastian, *Prakticka elektrotechnika*. Brno: Europa Sobotales, 2003. 304 p., ISBN 80-86706-15-X

- [5] X5. Erdei, Z., Dicso, L., A., Neamt, L., Chiver, O., Symbolic equation for linear analog electrical circuits using Matlab, WSEAS Transactions on Circuits and Systems, Issue 7, Vol. 9, July 2010, ISSN: 1109-2734