# 65 nm CMOS devices for Low Power Applications

KIRAN BAILEY<sup>1</sup>, K.S. GURUMURTHY<sup>2</sup> <sup>1</sup> Department of ECE, BMS college of Engineering, Bangalore, INDIA Email: kiranbailey@gmail.com <sup>2</sup> Department of ECE, UVCE, Bagalore University Bangalore, INDIA Email: drksgurumurthy@gmail.com

Abstract: This paper attempts to analyze the performance of 65 nm CMOS device structures for low power applications. It indicates that the historical trend of scaling of MOS devices can be sustained by innovative CMOS Structures such as Ultra-thin body SOI devices and multiple gate MOSFETS (such as FinFETS), that can withstand the adverse effects of Scaling. A particular issue of great concern in logic design is the power dissipation. For high- performance logic with increased leakage currents, chip static power dissipation is expected to become a bottleneck to meet aggressive targets for performance scaling. Innovations in circuit design and architecture for performance management as well as utilization of multiple transistors on chip are required for chip design. Multiple transistors having different threshold voltages (Vt) are used selectively with the low V<sub>t</sub>, high leakage devices being used mainly in the critical paths and higher V<sub>t</sub>, lower leakage devices being used in the rest of the chip area to control static power dissipation. This paper presents the low static power dissipation CMOS devices at 65 nm technology node and compares the performance of SOI CMOS with the conventional planar Bulk CMOS and establishes that SOI CMOS is better suited for low stand-by power applications. A low leakage current of 0.2 pA/µm for NMOS and 0.1 pA/µm for PMOS was observed for SOI devices at a supply voltage of 1.5V as compared to 10nA/µm for bulk CMOS devices at a supply voltage of 1.2V.

Keywords: Bulk CMOS, SOI MOSFET, MOS Scaling and Leakage currents.

1. Introduction: After more than three decades of relentless scaling of CMOS devices to nanometer dimensions for faster circuit operation, higher packing density and lower power dissipation, CMOS technology has now become the prevailing technology for VLSI applications. This scaling is driving the industry towards major technological innovations. including material and process changes such as Metal gates and High- k dielectrics and also new structures such as Ultra-Thin Body SOI and FinFETs. With Scaling of planar Bulk MOSFETs, Significant challenges such as high channel doping, Junction leakage due to band-to-band tunneling and various Short channel effects (SCE) need to be addressed. Also, random doping variations in the channel in extremely small MOSFETs lead to variability of threshold voltages. Another challenge for highly scaled MOSFETs is the increase in the Source/ Drain series resistance due to shallow junctions [1]-[3]. Due to the challenges with scaling of planar bulk MOSFETs, Novel device structures such as ultra-thin body SOI MOSFETs and multiple gate structures such as FINFETs are becoming attractive alternatives.

2. Proposed Devices for low power applications: A major portion of the semiconductor device production is devoted to digital logic. For low power logic, control of static power dissipation with scaling is the critical goal. To meet this goal, transistor leakage current is projected

to be much lower than that of highperformance logic. High- performance logic refers to chips of high speed and high power dissipation, such as Microprocessor unit chips. Low power logic refers to chips for mobile systems where the allowable leakage currents are limited by battery life. There are two major categories in low power i.e. Low operating power (LOP) and Low standby power (LSTP) logic [4]. LOP chips are used for relatively high performance mobile applications such as notebook computers and the focus is on reduced dynamic power dissipation. LSTP chips are used for lower performance. lower cost consumer applications such as cellular telephones. LSTP chips are characterized by low operating frequency and lower battery capacity. The main focus of LSTP chips is to have the lowest possible static power dissipation that means lowest possible leakage current. According to ITRS roadmap, the leakage current is projected at 30pA/µm for LSTP chips and is held relatively constant while for LOP, it is 9nA/µm and it increases slowly with scaling.

# **3.** 65 nm Simulation results and discussion: NMOS and PMOS devices at 65 nm technology node were simulated using Synopsys TCAD device simulator. The Drift Diffusion carrier transport model was used to carry out the simulations. The maximum supply voltage used for Bulk CMOS device simulations is 1.2V and for SOI MOSFETS it is 1.5V.

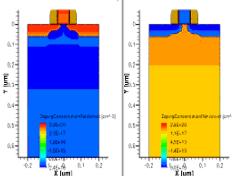

Bulk CMOS: The Bulk NMOS and PMOS devices at 65 nm were simulated with process enhancements such as retrograde channel doping and Halo implants to control short channel effects [5] .The leakage currents for these devices have been optimized for 10nA/um. The sub threshold slope was found to be approximately 150 mv/dec that indicates slow switching between logic states. Fig .1a and 1b shows the structure of the 65 nm bulk devices along with the Id-Vg curves that shows a good on current of 530  $\mu$ A/ $\mu$ m for NMOS and 367  $\mu$ A/ $\mu$ m for PMOS at a supply voltage of 1.2 V. The leakage current for both devices is approximately 10 nA/ $\mu$ m and hence these devices are more suitable for Low Operating Power (LOP) chips.

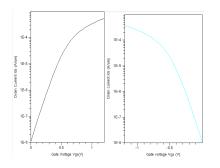

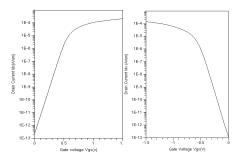

SOI CMOS: Fig .2a shows a 100nm buried oxide layer implanted in the silicon substrate for reduced SCE and a 50 nm silicon body incorporated for fully depleted SOI device with minimal doping in the channel for enhanced mobility. A higher doping in the range of 5e17 was implemented in the source/ drain extension regions to lower the off current and at the same time maintain the This doping has been drive current. introduced to minimize the width of the depletion layer and to control short channel effects. Different doping levels were introduced and simulated to find the optimum value which lowers the leakage current and also does not reduce the on state drive current. Fig 3 shows a graph of the Leakage current against the Doping Concentrations NE. It was found that a Boron Concentration of 7e+17/cm<sup>3</sup> was optimum for NMOS and Phosphorus concentration of  $4e+17/cm^3$  was optimum for PMOS. Further increasing the Doping concentration leads to drastic reduction in the drive current as is shown in table 1. A low sub threshold slope of 80 mv/dec for PMOS and 70 mv/dec for NMOS indicates good control of SCEs as seen in Fig.2b. A low leakage current of 0.2pA/µm for NMOS and 0.1pA/µm for PMOS makes these devices suitable for LSTP applications. Due

to the thin silicon body thickness for these devices, the resistance in the channel is high resulting in reduced drive currents.

Bulk CMOS 65 nm:

fig.1a: Bulk planar NMOS and PMOS device structures with 65 nm gate lengths.

fig.1b: The I-V curves show a leakage current of  $10nA/\mu m$  at a supply voltage of 1.2V.

## 0 <u>5</u> w 125 A3 -135 NE-NE ME-NE UTE-NT 04 ٨. 47546 145 445+4 606+15 -060 -Unit 1,5 -145 M a Mili 42 40 6 61 62 63 64 ġ, á. ů. in in in ) (un)

SOI CMOS 65 nm:

fig.2a: SOI NMOS and PMOS device structures with 65 nm gate lengths.

fig.2b: The I-V curves shows a leakage current of a few pA/ $\mu$ m at a supply voltage of 1.5V

fig 3. Leakage Current (A/um) Vs Doping Concentration (atoms/cm $^3$ ) in the Source/ Drain extension regions.

**4. Conclusion:** 65 nm P-channel and N-channel fully depleted SOI Devices with a body thickness of 50 nm were simulated and compared with bulk planar NMOS and PMOS devices for

low power applications. It was found that SOI devices require very light doping in the channel and short channel effects are controlled better in spite of lower channel doping. To control the short channel effects and to reduce the leakage currents, a constant doping in the range of 5e+17 was introduced in the source/drain extension regions. This was found to be effective in reducing the off currents. The off current for the SOI devices are about a few pA/µm whereas for bulk devices it is in the range of nA/µm. Thus it is shown in this paper that these low leakage current SOI devices can be used for LSTP chips used in mobile applications.

Table 1. A table showing the values of leakage currents Vs the doping concentration for SOI MOSFETS.

| Doping<br>Concentr<br>ation N <sub>E</sub><br>(atoms/<br>cm <sup>3</sup> ) | 1e+1<br>6        | 5e+16       | 1e+17         | 5e+17        | 1e+1<br>8          |

|----------------------------------------------------------------------------|------------------|-------------|---------------|--------------|--------------------|

| PMOS                                                                       | 6nA/<br>μm       | 1nA/μm      | 0.16nA/<br>μm | 0.1pA/<br>μm | 0.002<br>pA/<br>μm |

| NMOS                                                                       | 129n<br>Α/<br>μm | 50nA/<br>μm | 5nA/<br>μm    | 0.2pA/<br>μm | 0.05<br>pA/<br>μm  |

# 5. References:

[1]. Yuan Taur, Douglas A. Buchanan, Wei Chen, David J. Frank, Khalid E. Ismail, Shin-Hsien Lo, George A. Sai-Halasz, Raman G. Vishwanathan, Hsing-Jen C. Wann, Shalom J. Wind and Hon-Sum Wong, "CMOS Scaling into the Nanometer Regime", Proceedings of the IEEE, Vol. 85, No. 4, April 1997. [2]. Chenming Hu, "Future CMOS Scaling and Reliability", Proceedings of the IEEE, Vol. 81, No.5, May 1993.

[3]. Ghavam G. Shahidi, "Challenges of CMOS Scaling below 0.1um", The 12<sup>th</sup> International Conference on Microelectronics, Tehran, Oct, 31- Nov,2 2000.

[4]. The International Technology Roadmap for Semiconductors, 2007 edition.

[5]. James D. Plummer, Micheal D. Deal and Peter B. Griffin, "Silicon VLSI Technology- Fundamentals, Practice and Modeling ".